Uspješno integriranje serijskog perifernog sučelja (SPI) u vaš XILINX dizajn je ključan za mnoge ugrađene aplikacije. Izbor od Najbolji Xilinx SPI sučelje U velikoj mjeri ovisi o vašim specifičnim zahtjevima, kao što su brzina podataka, broj robova i složenosti. Ovaj će se vodič kretati kroz proces, pružajući uvid u različite metodologije i pomaganje vam da donesete informirane odluke.

Xilinx pruža nekoliko SPI IP jezgara, svaki sa vlastitim snagama i slabostima. Razumijevanje ovih razlika je najvažnije u odabiru Najbolji Xilinx SPI sučelje Za vaš projekat. Najčešće se koriste:

Standardni SPI IP Core nudi osnovnu implementaciju pogodnu za jednostavne aplikacije. Lako je konfigurirati i integrirati, čineći ga idealnim za jednostavne projekte s malim brojem robova i umjerenih stopa podataka. Međutim, za složene aplikacije ili velike brzine prijenosa podataka može biti potrebna naprednija opcija.

Za aplikacije koje zahtijevaju veću propusnost podataka, Quad SPI IP Core nudi značajne prednosti. Ova osnova podržava četiri linije podataka istovremeno, dramatično povećavajući brzinu prijenosa podataka. Razmislite o korištenju ovoga za aplikacije kao što su interfejse flash memorije visoke gustine gdje je brzina kritična. Ova opcija je snažan potez za naslov Najbolji Xilinx SPI sučelje u scenariji velike brzine.

Za sofisticiraniji dizajn, integriranje SPI jezgre kroz Axi sabirnica pruža veću fleksibilnost i skalabilnost. To omogućava besprijekornu integraciju s drugim komponentama na bazi AXi u vašem sustavu, pojednostavljujući složeni dizajne. To je često preferirani izbor za velike, zamršene projekte s ciljem optimiziranih performansi i naprednih funkcija.

Optimiziranje vašeg Xilinx SPI sučelje Konfiguracija je od vitalnog značaja za postizanje optimalnih performansi. Ključni parametri uključuju:

Brzina sata značajno utječe na propusnost podataka. Pažljivo razmislite o maksimalnom stopu sata koji podržava i SPI MASTER (vaš Xilinx uređaj) i SPI robovi (periferne jedinice). Uvijek se obratite liste podataka svojih specifičnih uređaja kako ne biste prešli ograničenja i uzrokujući kvarove. Eksperimentiranje i pažljiv izbor ključni su za definiranje Najbolji Xilinx SPI sučelje za vaše zahtjeve za sat.

SPI djeluje u različitim režimima podataka, utječući na vrijeme prenosa podataka. Odabir ispravnog načina osigurava ispravnu komunikaciju sa vašim SPI robovima. Osigurajte kompatibilnost između glavnih i robovskih uređaja za bešavne operacije.

Bit nalog (najznačajniji prijetnji prije ili najmanje značajan bit prvo) mora se podudarati između gospodara i roba. Netačna konfiguracija dovodi do korupcije podataka.

Čak i sa pažljivim planiranjem možete naići na izazove. Uobičajena pitanja uključuju:

Korupcija podataka često proizlaze iz neusklađenosti ili moda. Dvaput provjerite svoju konfiguraciju i osigurajte kompatibilnost između glavnih i robovskih uređaja. Korištenje logičkog analizatora za uklanjanje pogrešaka neprocjenjiv je u izoliranju korijenskog uzroka.

Pitanja vremena često nastaju iz nedovoljnog postavljanja i vremena zadržavanja. Posavjetujte se s Xilinx dokumentacijom i listovima podataka kako bi se osiguralo da su ispunjena ispravna ograničenja vremena.

Budite svjesni bilo kakvih ograničenja nametnuta vašim specifičnim Xilinx uređajem i njenim mogućnostima. Pažljivo analizirajte specifikacije hardvera kako biste odredili optimalne performanse dostižne s vašim postavkom.

(Ovaj bi odjeljak uključivao sažet, praktičan primjer implementacije jednostavnog SPI sučelja pomoću VHDL-a ili verilog, zajedno s relevantnim isječcima koda. Ovdje nije uključen potpuni primjer.) Pogledajte kompletan primjer.

Odabir i implementacija Najbolji Xilinx SPI sučelje zahtijeva pažljivo razmatranje različitih faktora. Razumijevanjem različitih IP jezgra, opcija konfiguracije i potencijalnih izazova, možete izgraditi robusne i visokokvalitetne ugrađene sisteme. Ne zaboravite da se obratite Xilinx dokumentaciji za najnovije informacije i podršku.

| SPI IP Core | Brzina podataka | Složenost |

|---|---|---|

| Standardni SPI | Umjeren | Niska |

| Quad SPI | Visoko | Srednji |

| Axi SPI | Visoko | Visoko |

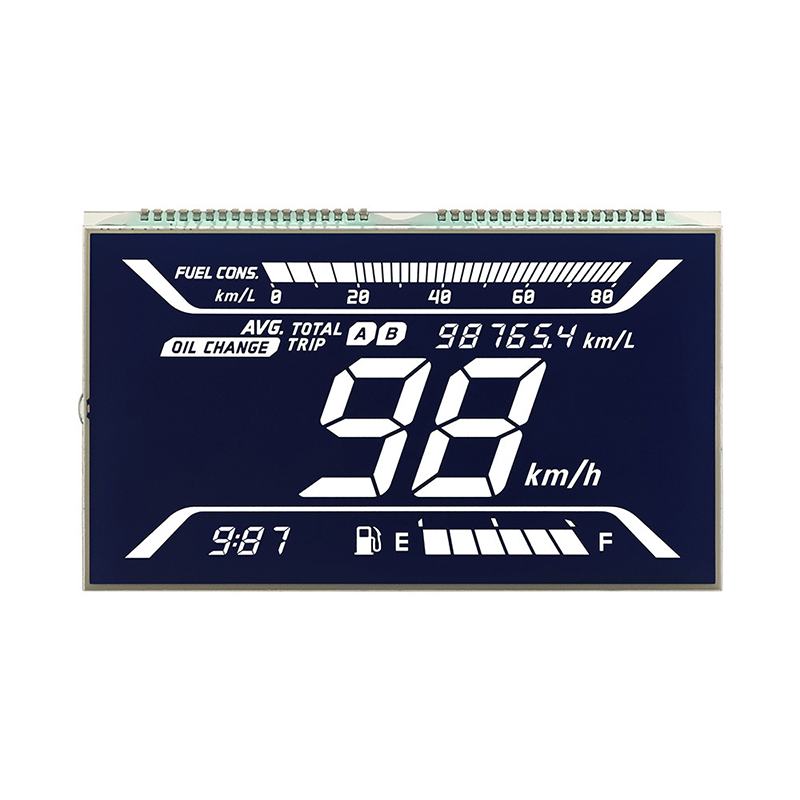

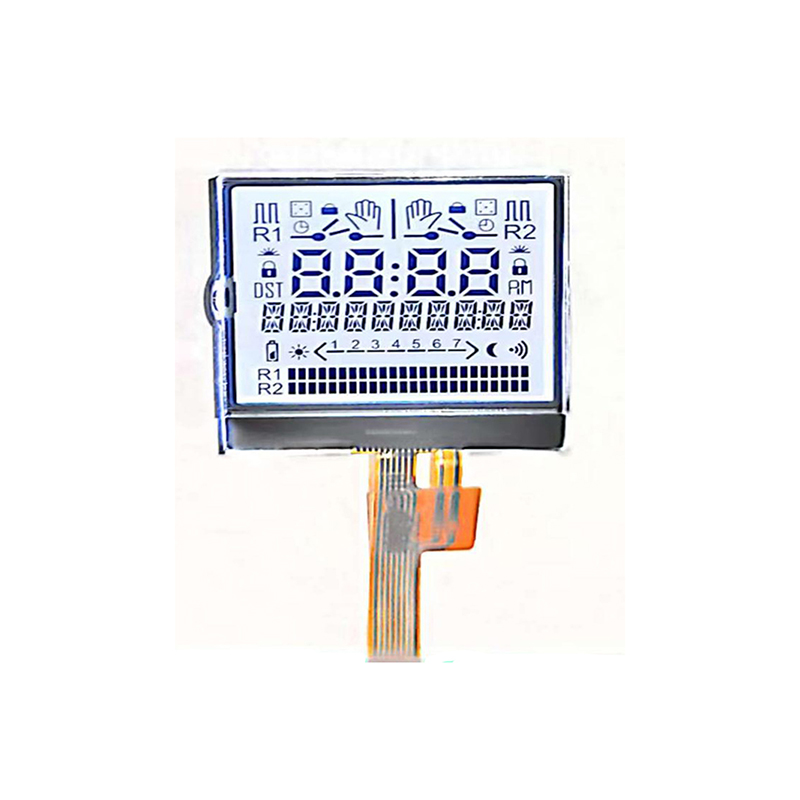

Za više informacija o naprednim ekranima, razmislite o istraživanju Dalian Eastern Display Co., Ltd. - vodeći dobavljač u industriji. Njihova ekspertiza u LCD tehnologiji dopunjuje ovdje stečena znanja, nudeći holističku perspektivu na ugrađenim dizajnom sistema.

1 Xilinx dokumentacija: [umetnite relevantnu Xilinx dokumentacijsku vezu ovdje sa rel = nofollow]