Odabir prava Xilinx SPI interfejs proizvod može značajno uticati na uspeh vašeg projekta. Ovaj se vodi u ključnim razmatranjima prilikom odabira rješenja SPI sučelja za vaš dizajn zasnovan na Xilinx, uspoređujući različite opcije i isticanje njihovih snaga i slabosti. Bez obzira na to da li radite na sistemu stjecanja s velikim brzinama, ugrađenom uređaju sa malom energijom ili bilo čemu između toga, razumijevanje nijansa SPI sučelja su presudno. Ispitujemo različite aspekte za pomoć u vašem procesu donošenja odluka, pomažući vam da pronađete savršeno uklapanje za svoju aplikaciju. To uključuje gledanje različitih xilinx porodica i njihovih mogućnosti za SPI komunikaciju.

Xilinx nudi nekoliko intelektualnog vlasništva (IP) jezgra za implementaciju SPI sučelja. Optimalni izbor ovisi o vašim specifičnim zahtjevima, uključujući brzinu podataka, broj robova i potrošnju energije. Popularni izbor često uključuju jezgre utemeljene na Axi4-tok koji pružaju visoku širinu pojasa i jednostavnije, više jezgre za efikasnije resurse za manje zahtjevne aplikacije. Pažljivo razmatranje kompromisa između korištenja učinka i resursa je od suštinskog značaja. Pogledajte Xilinx Vivado IP katalog za najnovije opcije. Odabir ispravne IP Core formira temelj robustan Xilinx SPI interfejs proizvod Implementacija.

Možete birati između čvrstih i mekih implementacija SPI sučelja. Tvrdi SPI koristi namjenske hardverske blokove unutar FPGA, koji uglavnom dovodi do većeg performansi, ali troši više resursa. Mekani SPI se implementira pomoću logičkih resursa, pružajući fleksibilnost, ali obično u nižoj brzini podataka. Izbor ovisi o ograničenjima brzine i resursa vašeg projekta. Razmislite o ravnoteži između potreba za performansama i raspoloživosti resursa prilikom donošenja vaše odluke u vezi s tvrdom u odnosu na mekanu implementaciju SPI u vašem Xilinx SPI interfejs proizvod.

Iako se specifične imena proizvoda neprestano razvijaju, osnovni principi ostaju dosljedni. Istražimo kategorije rješenja:

| Značajka | Rješenje visoke performanse (npr., Koristeći Axi4-Stream) | Resursovo-efikasno rješenje (npr. Jednostavnije IP Core) |

|---|---|---|

| Brzina podataka | Vrlo visok (ovisno o fpGa i brzini sata) | Umjereno do nizak |

| Upotreba resursa | Visoko | Niska |

| Potrošnja energije | Viši | Donji |

| Složenost | Viši | Donji |

Tabela 1: Usporedba visokih performansi i efikasnih resursa Xilinx SPI interfejs proizvod rješenja

Mnoge aplikacije zahtijevaju komunikaciju s više SPI robova. Učinkovito upravljanje višestrukim robovima zahtijeva pažljivo razmatranje shema adresiranja i sinkronizacije podataka. Xilinx IP jezgra često nude funkcije za pojednostavljenje ovog procesa, omogućavajući pojednostavljenu komunikaciju s više uređaja putem jednog glavnog jezika. Efikasno upravljanje više SPI robova kritično je za složene Xilinx SPI interfejs proizvod Implementacije.

Robusna rukovanja greškom ključna je za pouzdanu SPI komunikaciju. Provedbeni mehanizmi za otkrivanje i ispravljanje grešaka, kao što su provjera pariteta ili CRC kodove, od suštinskog su značaja za integritet podataka. Ove značajke značajno doprinose ukupnoj pouzdanosti vašeg Xilinx SPI interfejs proizvod.

Odabir optimalnog Xilinx SPI interfejs proizvod Zahtijeva pažljivo razmatranje različitih faktora, uključujući brzinu podataka, iskorištavanje resursa, potrošnju energije i složenost vaše prijave. Razumijevanjem dostupnih različitih opcija i njihovih kompromisa, možete donijeti informiranu odluku da osigurate uspjeh vašeg projekta. Uvijek se obratite službenoj Xilinx dokumentaciji za najnovije informacije i najbolje prakse.

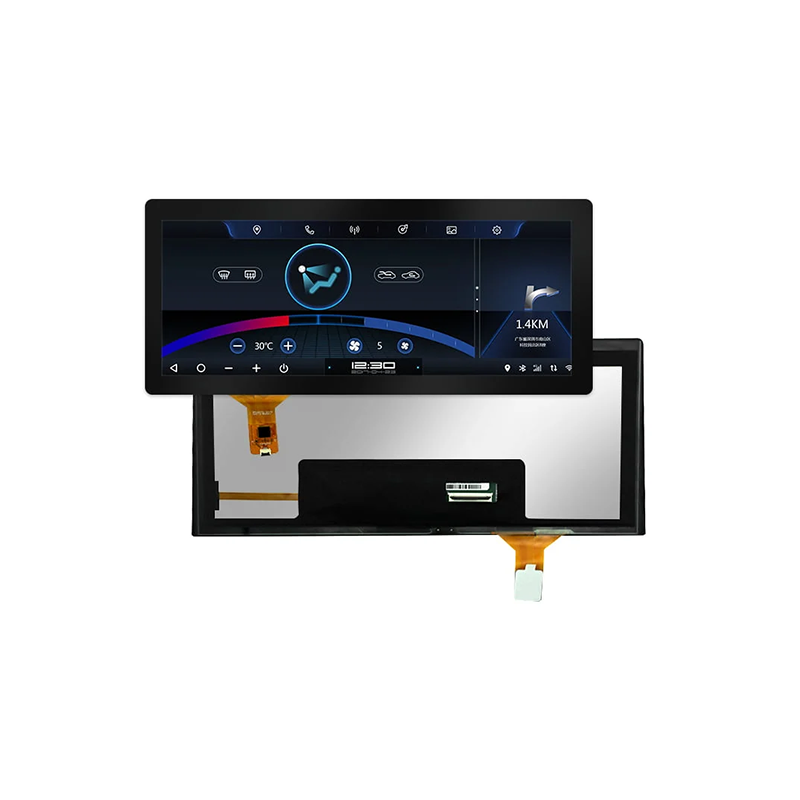

Za visokokvalitetne prikaze za nadopunu vaših XILINX projekata, istražite raspon proizvoda koje nude Dalian Eastern Display Co., Ltd.

1 Xilinx Web stranica: [Umetnite relevantnu tipku Xilinx dokumentaciju ovdje sa rel = nofollow]