Dieser Leitfaden enthält eine detaillierte Erklärung derCPLD SPI -Schnittstelle, um seine Grundlagen, praktischen Anwendungen und potenziellen Herausforderungen zu decken. Erfahren Sie, wie Sie die SPI -Kommunikation mit CPLDs effektiv konfigurieren und für verschiedene Designs eingebettete Systeme verwenden. Wir werden verschiedene Aspekte untersuchen, von grundlegenden Konzepten bis hin zu fortgeschrittenen Techniken, um sicherzustellen, dass Sie ein solides Verständnis dieser entscheidenden Schnittstelle haben.

Die serielle periphere Grenzfläche (SPI) ist ein synchroner, full-Duplex-Kommunikationsinbus, der für die Kurzstreckenkommunikation verwendet wird, hauptsächlich in eingebetteten Systemen. Es zeichnet sich durch Einfachheit und Geschwindigkeit aus und macht es zu einer beliebten Wahl für die Verbindung von Mikrocontrollern, Sensoren und anderen Peripheriegeräten. Ein wesentlicher Vorteil ist die relativ niedrige Zählung im Vergleich zu anderen Schnittstellen.

DerCPLD SPI -SchnittstelleVerwendet normalerweise vier Signallinien:

Die richtige Hardwarekonfiguration ist für eine erfolgreiche entscheidendeCPLD SPI -Schnittstelle. Dies beinhaltet die Auswahl geeigneter CPLD -Stifte für jedes Signal, die Sicherung der korrekten Spannungsniveaus und die Berücksichtigung der Signalintegrität. Die Wahl der CPLD hängt von der Komplexität Ihrer Anwendung und der erforderlichen Leistung ab.

Die Softwarekonfiguration umfasst die Programmierung der CPLD, um korrekt auf SPI -Befehle zu reagieren. Dies umfasst häufig die Konfiguration bestimmter Register innerhalb der CPLD, um die Datenübertragungs- und Steuersignale zu verarbeiten. Die Einzelheiten variieren je nach Architektur der CPLD und der ausgewählten Programmiersprache (z. B. VHDL, Verilog).

Betrachten wir ein Szenario, in dem Sie eine Xilinx -CPLD verwenden. Der Prozess würde beinhalten:

Detaillierte Beispiele und Codeausschnitte finden Sie in der Xilinx -Dokumentation und verschiedenen Online -Ressourcen. Denken Sie daran, die Datenblätter für Ihre spezifische CPLD für genaue PIN -Zuordnungen und Registrierungskonfigurationen zu konsultieren.

Verschiedene SPI-Modi (Modi 0-3) definieren die Taktpolarität und Phase und beeinflussen den Zeitpunkt der Datenübertragung. Das Verständnis dieser Modi ist für die Einrichtung der korrekten Kommunikation von wesentlicher Bedeutung. Ihr Mikrocontroller und Ihr CPLD müssen so konfiguriert sein, dass der gleiche SPI -Modus verwendet wird.

Das Implementieren einer robusten Fehlerbehandlung ist in jedem Kommunikationssystem von entscheidender Bedeutung. Dies kann Paritätsprüfungen, Überprüfungen oder andere Mechanismen für Fehlererkennung und Korrektur umfassen. Die Gewährleistung der Datenintegrität ist von größter Bedeutung, insbesondere in kritischen Anwendungen.

Für Hochgeschwindigkeitsanwendungen ist es von entscheidender Bedeutung, die Taktfrequenz zu optimieren und die Signalintegrität sorgfältig zu berücksichtigen (z. B. die Minimierung der Spurenlängen und die Verwendung einer angemessenen Beendigung). Hochgeschwindigkeits-SPI kann fortschrittliche Techniken wie differentielle Signalübertragung erfordern.

Fehlerbehebung bei einer FehlfunktionCPLD SPI -SchnittstelleBeinhaltet häufig die systematische Überprüfung von Hardwareverbindungen, Softwarekonfiguration und Signalintegrität. Die Verwendung von Logikanalysatoren oder Oszilloskopen kann von unschätzbarem Wert sein, um Zeitprobleme oder Datenbeschädigung zu identifizieren.

Denken Sie daran, immer die Datenblätter Ihres spezifischen CPLD und Ihres Microcontroller für detaillierte Informationen und bestimmte Anweisungen zu konsultieren. Dieser umfassende Leitfaden bietet eine starke Grundlage für das Verständnis und die Beherrschung derCPLD SPI -SchnittstelleSie befähigen Sie, robuste und effiziente eingebettete Systeme zu entwerfen.

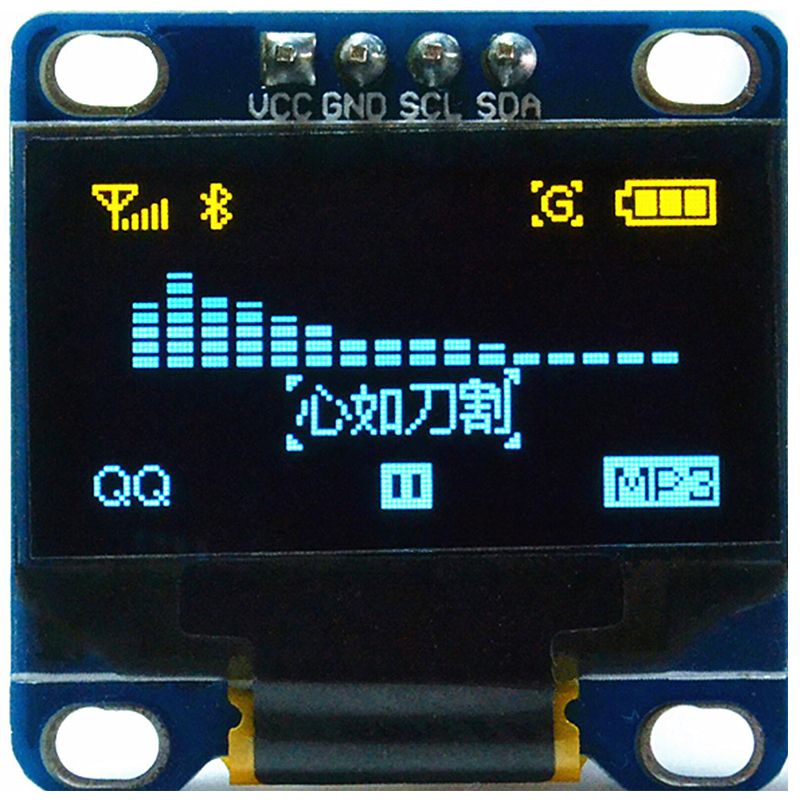

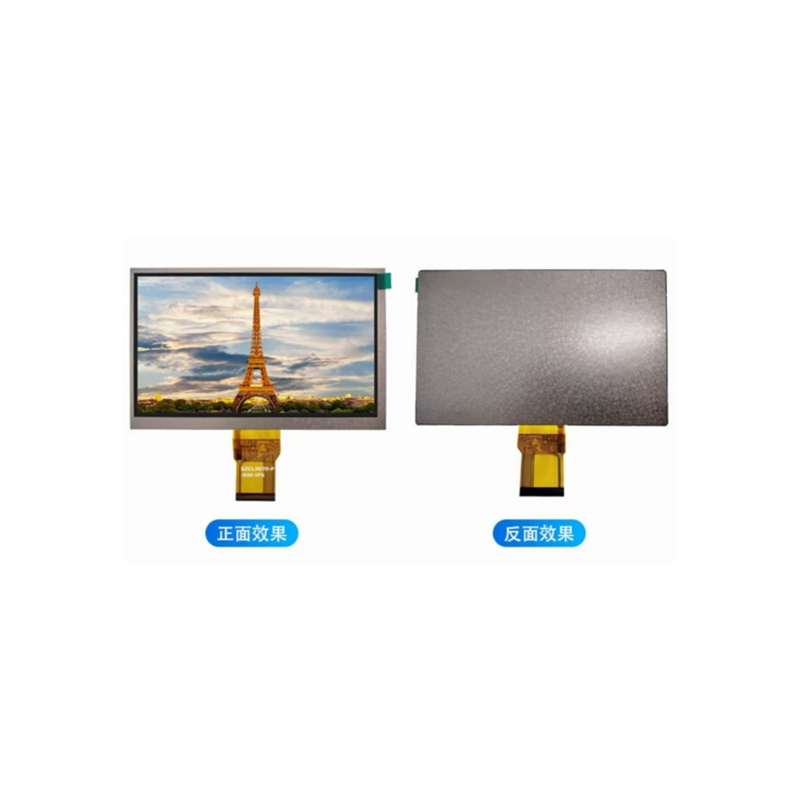

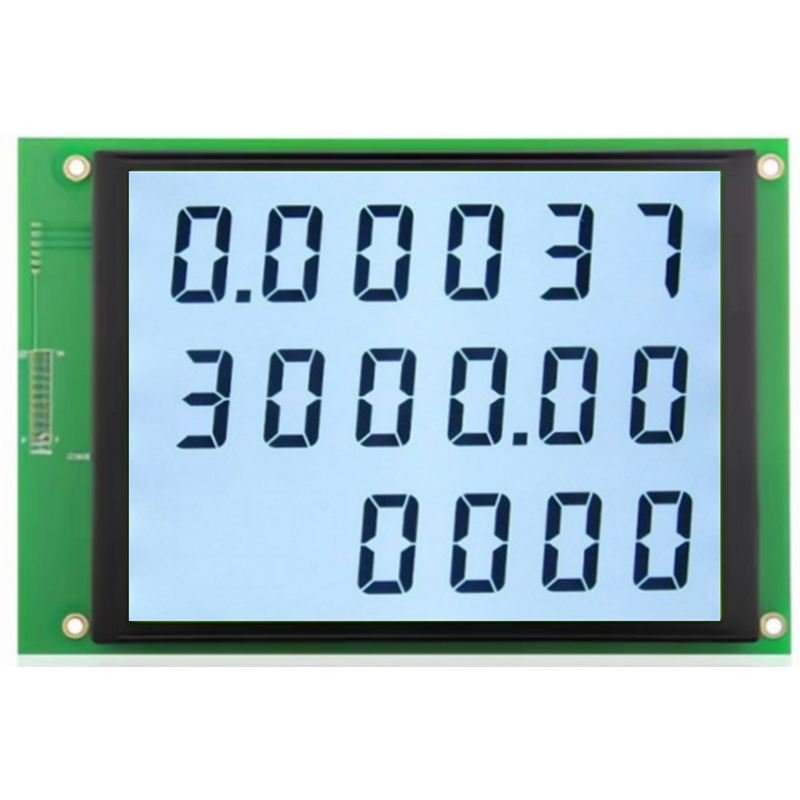

Für qualitativ hochwertige LCD-Displays, um in Ihre CPLD-Projekte integriert zu werden, sollten Sie die Optionen untersuchenDalian Eastern Display Co., Ltd.Sie bieten eine breite Palette von Displays, die für verschiedene Anwendungen geeignet sind.