Dieser Leitfaden bietet einen umfassenden Überblick über die serielle periphere Schnittstelle (SPI) und ihre Implementierung in Feldprogrammiergate-Arrays (FPGAs). Wir werden die Grundlagen der SPI-Kommunikation behandeln, verschiedene Designansätze für FPGA-basierte SPI-Schnittstellen untersuchen und in praktische Beispiele und Tipps zur Fehlerbehebung eingehen. Erfahren Sie, wie Sie SPI -Peripheriegeräte effizient in Ihre FPGA -Projekte integrieren und die Leistung für verschiedene Anwendungen optimieren.

Der SPI-Bus ist eine synchrone serielle Kommunikationsschnittstelle mit vollem Duplex, die häufig für die Kommunikation mit kurzer Entfernung verwendet wird. Es wird vier Hauptsignale verwendet: Mosi (Master Out Slave In), Miso (Master in Slave Out), SCK (Serienuhr) und SS/CS (Slave Select/Chip Select). Das Verständnis der Rollen jedes Signals ist für erfolgreiche entscheidendFPGA SPI -SchnittstelleDurchführung. Die Daten werden Bit für Bit übertragen, wobei das Taktsignal die Datenübertragung synchronisiert wird. Mit der Slave -Auswahllinie wird ein bestimmtes Slave -Gerät im Bus ausgewählt. Es gibt unterschiedliche SPI -Modi, die durch die Einstellungen der Taktpolarität (CPOL) und Phase (CPHA) definiert sind, und beeinflussen, wie Daten am Taktrand abgetastet werden.

Es gibt vier Haupt -SPI -Modi (Modus 0 bis Modus 3), die von den CPOL- und CPHA -Einstellungen bestimmt werden. Diese Einstellungen beeinflussen, wenn Daten während des Taktzyklus abgetastet werden. Die Auswahl des richtigen Modus ist für die Kommunikation mit bestimmten SPI -Peripheriegeräten unerlässlich. Eine falsche Modusauswahl führt zu einer falschen Datenübertragung. Die folgende Tabelle beschreibt die verschiedenen Modi:

| Modus | CPOL | CPHA | Beschreibung |

|---|---|---|---|

| Modus 0 | 0 | 0 | Die Leerlaufuhr ist niedrig, Daten werden am steigenden Rand abgetastet. |

| Modus 1 | 0 | 1 | Die Leerlaufuhr ist niedrig, Daten werden am fallenden Rand abgetastet. |

| Modus 2 | 1 | 0 | Die Leerlaufuhr ist hoch, die Daten werden am steigenden Rand abgetastet. |

| Modus 3 | 1 | 1 | Die Leerlaufuhr ist hoch, die Daten werden am fallenden Rand abgetastet. |

Implementierung anFPGA SPI -SchnittstelleBeinhaltet das Entwerfen eines Moduls, das mit den SPI -Peripheriegeräten interagiert. Dies beinhaltet in der Regel die integrierte Logikblöcke des FPGA, um eine Statusmaschine zu erstellen, die das SPI-Kommunikationsprotokoll verwaltet. Erwägen Sie die von Ihrem FPGA -Anbieter bereitgestellte IP -Kerne für vereinfachtes Design und optimierte Leistung. Diese Kerne bieten häufig Funktionen wie DMA-Unterstützung für die Hochgeschwindigkeitsdatenübertragung.

Das Design wird je nach Präferenz und den von Ihnen verwendeten Tools entweder mit Verilog oder VHDL implementiert. Der Code verwaltet die vier SPI -Signale und verarbeitet die Datenübertragung basierend auf dem ausgewählten SPI -Modus. Eine gut strukturierte Zustandsmaschine ist entscheidend für den Umgang mit verschiedenen Phasen der Kommunikation, z. Fehlerbehebung und robustes Design sind wichtig, um eine zuverlässige Kommunikation zu gewährleisten.

Betrachten Sie für die Hochgeschwindigkeitsdatenübertragung Techniken wie die Verwendung mehrerer SPI-Schnittstellen oder die Verwendung fortschrittlicher Funktionen, die Ihr FPGA anbietet, wie z. B. dedizierte Serienschnittstellen mit Hochgeschwindigkeit oder DMA-Controller. Bei höheren Frequenzen ist eine sorgfältige Berücksichtigung der Signalintegrität von entscheidender Bedeutung, um Signalverzerrungen und Datenfehler zu vermeiden.

Um mehrere SPI -Sklaven zu unterstützen, müssen mehrere Sklavenauswahlzeilen verwaltet werden. Dies kann durch einen Multiplexer oder durch Zuweisen separater SPI -Instanzen jedem Sklaven erreicht werden. Das ordnungsgemäße Verwalten der Slave -Select -Signale ist wichtig, um Konflikte zwischen mehreren Sklavengeräten zu vermeiden.

DebuggenFPGA SPI -SchnittstelleProbleme können schwierig sein. Die Verwendung von Logikanalysatoren und Debugging -Tools, die von Ihrer FPGA -Entwicklungsumgebung bereitgestellt werden, sind von unschätzbarem Wert. Überprüfen Sie immer Ihre SPI -Moduseinstellungen, Taktfrequenzen und Signalintegrität, um eine ordnungsgemäße Kommunikation zu gewährleisten. Nach den Best Practices für digitales Design, wie beispielsweise klare Signal -Namens -Konventionen und modulares Design, verbessert die Wartbarkeit und Debugierbarkeit Ihres Projekts erheblich.

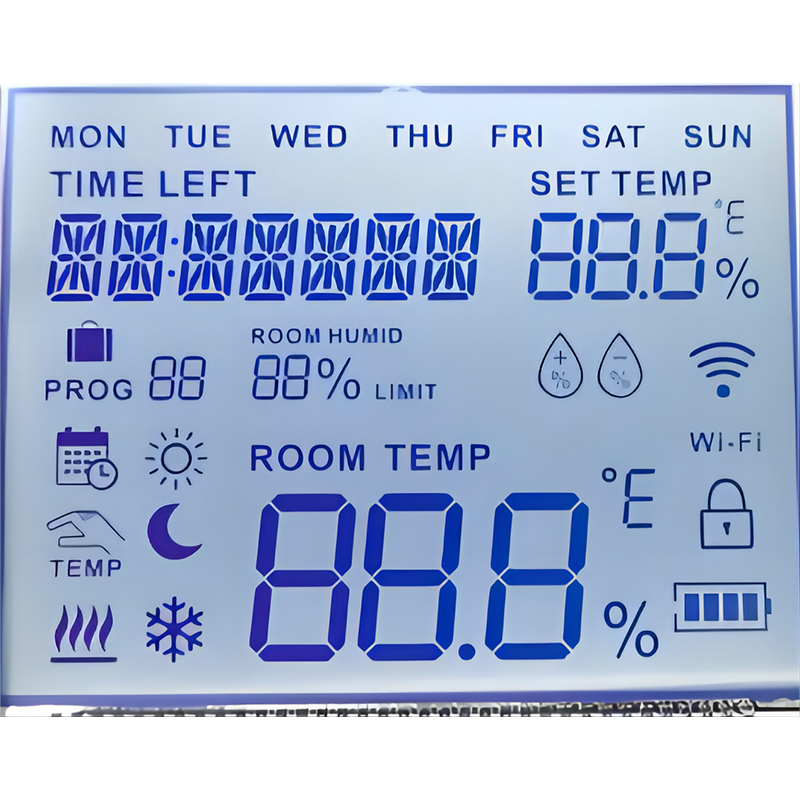

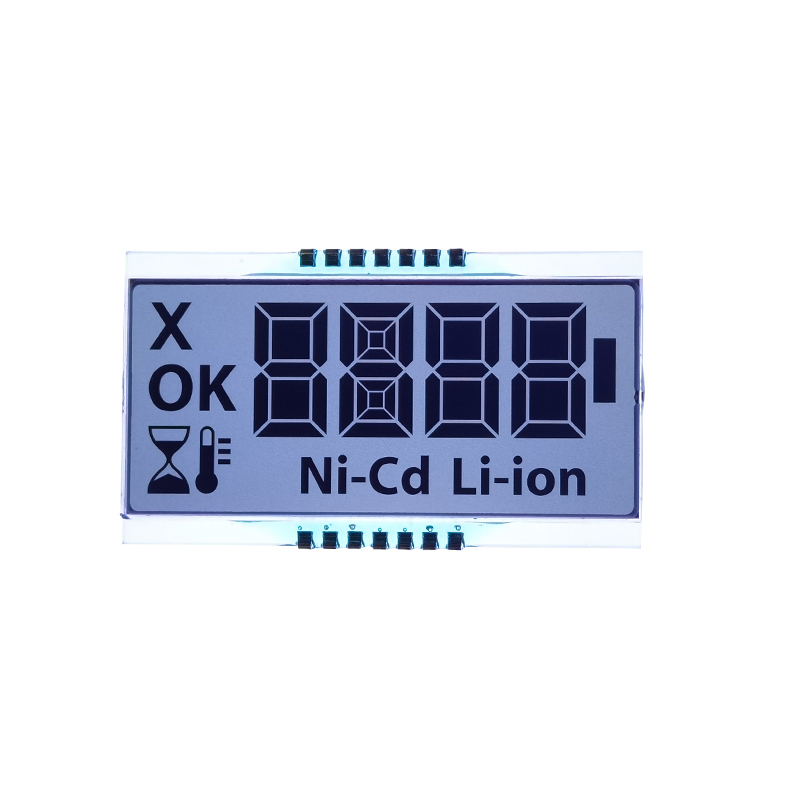

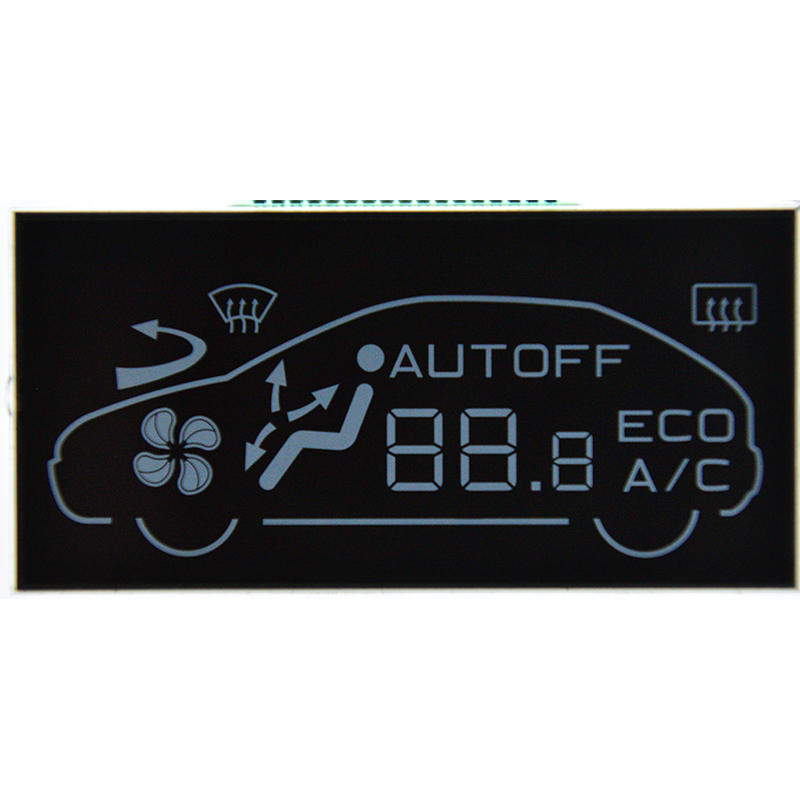

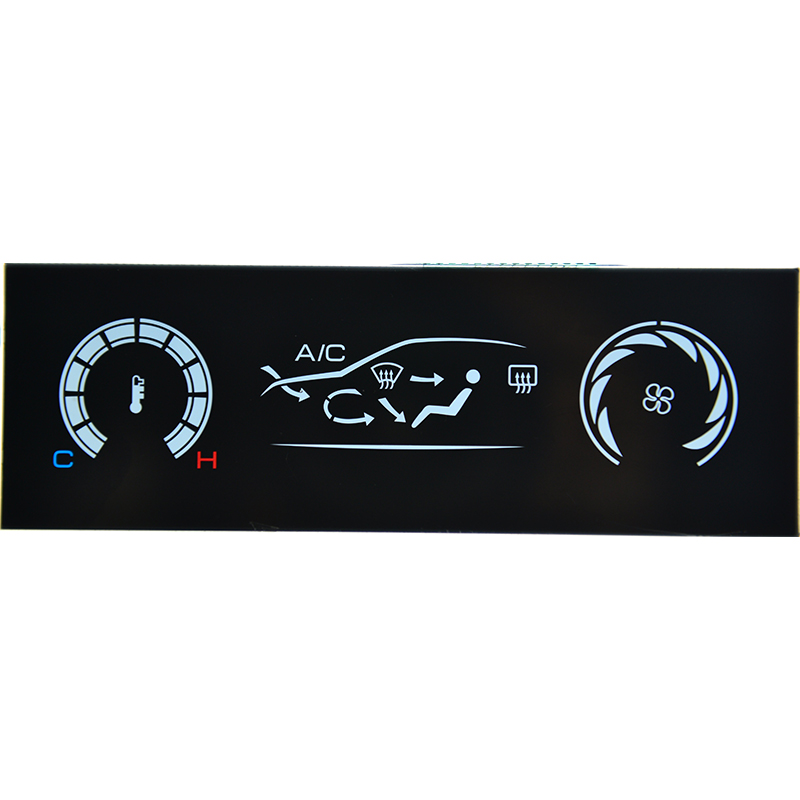

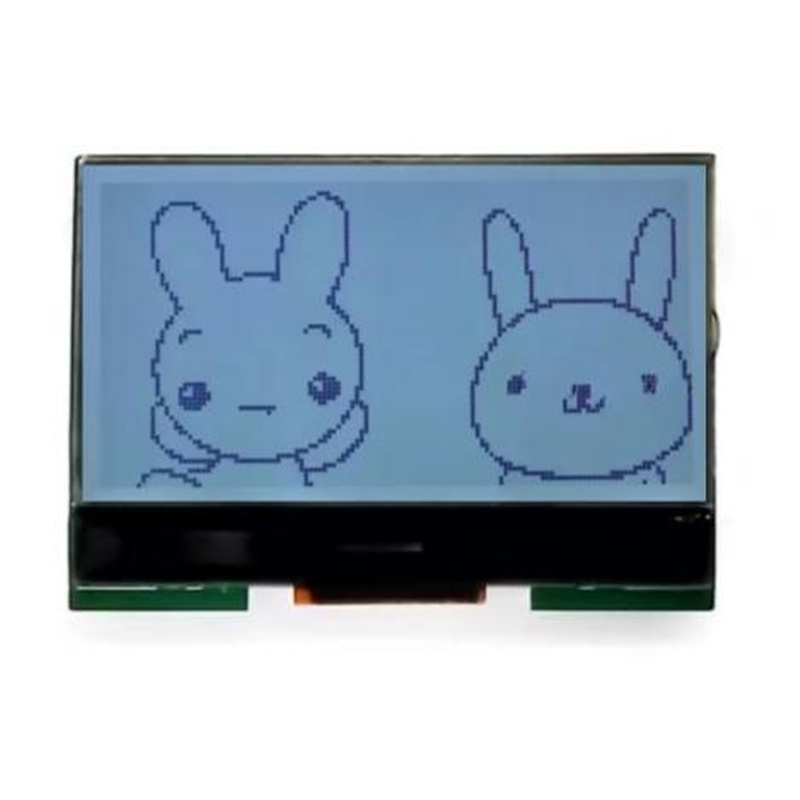

Weitere Informationen zu LCD -Anzeigen und verwandten Technologien finden Sie möglicherweise die Ressourcen beiDalian Eastern Display Co., Ltd.hilfreich. Sie bieten eine breite Palette von Display -Lösungen, die häufig die SPI -Kommunikation verwenden.

Referenzen:

1[Fügen Sie hier Ihre Referenz hinzu, wenn Sie externe Quellen verwendet haben]