Xilinx SPI -Schnittstelle: Ein umfassendes Leitfadenverständnis und Implementieren der Xilinx -SPI -Schnittstelle für effiziente Datenübertragung, bietet einen umfassenden Überblick über die serielle periphere Schnittstelle (SPI) in Xilinx -Geräten, die deren Funktionalität, Implementierung und Best Practices für einen effizienten Datentransfer abdecken. Wir werden verschiedene Aspekte untersuchen, von grundlegenden Konzepten bis hin zu fortgeschrittenen Techniken, mit denen Sie das volle Potenzial von nutzen könnenXilinx SPI -Schnittstellein Ihren Designs. Wir werden uns mit Konfigurationen befassen, gemeinsame Probleme beheben und die Leistung für verschiedene Anwendungen optimieren.

Verständnis der Xilinx SPI -Schnittstelle

SPI -Grundlagen

Die serielle periphere Grenzfläche (SPI) ist ein synchrones, umfassendes Kommunikationsprotokoll für die Kommunikation mit kurzer Entfernung. Es handelt sich um eine Vier-Draht-Schnittstelle, die typischerweise aus: Mosi (Master Out Sklave In): Daten vom Master an den Sklaven gesendet werden. Miso (Meister im Sklavenausgang): Daten, die vom Sklaven an den Master gesendet wurden. SCLK (Serienuhr): Taktsignal -Synchronisierungsdatenübertragung. SS (Slave Select): Wird verwendet, um einzelne Sklaven im Bus auszuwählen. Xilinx FPGAs bietet flexible und konfigurierbare SPI -Controller, die eine nahtlose Integration in verschiedene Peripheriegeräte ermöglichen. Die spezifischen Implementierungsdetails können je nach der Xilinx -Gerätefamilie (z. B. Zynq, Kintex, Artix) und dem ausgewählten IP -Kern variieren.

Xilinx SPI IP -Kern

Xilinx bietet einen leicht verfügbaren und hochkonfigurierbaren SPI -IP -Kern in der Vivado Design Suite. Dieser Kern vereinfacht den Integrationsprozess durch Bereitstellung von vorgefertigten Modulen für verschiedene SPI-Modi und -Funktionen. Zu den wichtigsten Funktionen gehören: Konfigurierbare Datenbreite: Ermöglicht die Anpassung, die Datenbreite der angeschlossenen Peripheriegeräte zu entsprechen. Mehrere SPI-Modi: Unterstützt verschiedene SPI-Modi (Modus 0-3), um die Kompatibilität mit einer Vielzahl von Geräten zu gewährleisten. Loopback -Modus: Erleichtert das Testen und Debuggen, indem Daten Loopback im Kern aktiviert werden. Interrupt-Unterstützung: Ermöglicht eine effiziente Interrupt-Handhabung für Echtzeitanwendungen. Dieser IP-Kern verkürzt die Entwicklungszeit und -aufwand im Vergleich zur manuellen Implementierung erheblich.

Implementierung der Xilinx SPI -Schnittstelle

Hardwarekonfiguration

Implementierung der

Xilinx SPI -SchnittstelleBeinhaltet das Anschließen des SPI -IP -Kerns mit den gewünschten Peripheriegeräten und der Konfiguration seiner Parameter innerhalb der Vivado -Design -Suite. Dies umfasst die Auswahl des entsprechenden SPI -Modus, der Datenbreite und der Taktfrequenz. Sorgfältige Überlegungen zur Überkreuzung der Signalintegrität und der Taktdomänenüberschreitung, insbesondere wenn die Übertragung von Daten zur Hochgeschwindigkeitsdaten beteiligt ist.

Softwarekonfiguration

Der Softwaretreiber für die SPI -Schnittstelle umfasst in der Regel das Schreiben und Lesen von Datenregistern, die dem SPI -IP -Kern zugeordnet sind. Dies kann eine Hardware-Abstraktionsschicht (HAL) oder einen bestimmten Treiber verwenden, der von Xilinx oder einem Anbieter von Drittanbietern bereitgestellt wird. Die ordnungsgemäße Handhabung von Interrupts und Fehlerbedingungen ist für den zuverlässigen Betrieb von entscheidender Bedeutung.

Fortgeschrittene Techniken und Optimierung

DMA -Übertragung

Bei Anwendungen mit hohem Durchsatz steigert die Verwendung von DIME-Speicherzugriff (DMA) die Leistung erheblich, indem die Datenübertragung von der CPU abgeladen wird. Xilinx bietet DMA -Controller, die in den SPI -IP -Kern integriert werden können, um erhebliche Geschwindigkeitsverbesserungen zu erzielen.

Uhr Synchronisation

Eine präzise Taktsynchronisation ist für eine zuverlässige Datenübertragung von entscheidender Bedeutung, insbesondere bei höheren Frequenzen. Techniken wie CDC -Methoden (Clock Domain Crossing) müssen sorgfältig implementiert werden, um Metastabilitätsprobleme zu verhindern.

Fehlerbehebung und Best Practices

| Ausgabe | Mögliche Ursache | Lösung |

| Keine Datenübertragung | Falscher SPI -Modus, Verkabelungsfehler, Uhrprobleme | Überprüfen Sie die SPI |

| Datenbeschädigung | Uhrprobleme, Rauschen, falsche Datenbreite | Verbesserung der Taktstabilität, Hinzufügen von Abschirmung, Überprüfen Sie die Einstellungen für die Datenbreite |

Denken Sie daran, die offizielle Xilinx-Dokumentation für die aktuellsten Informationen und Best Practices zu konsultieren. Dieser detaillierte Leitfaden sollte Sie mit dem Wissen ausstatten, das erforderlich ist, um das effektiv zu nutzen

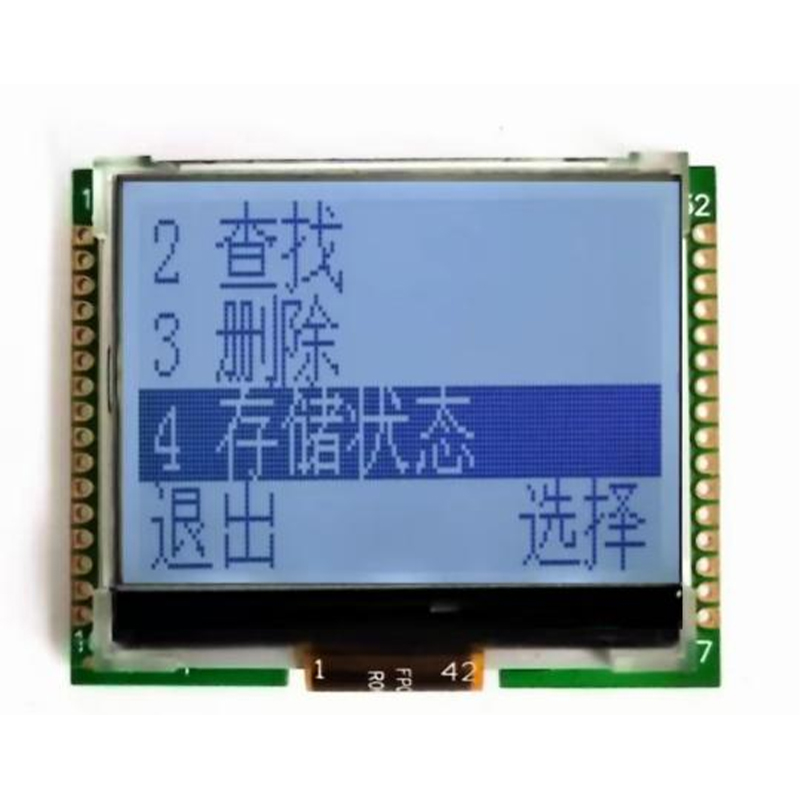

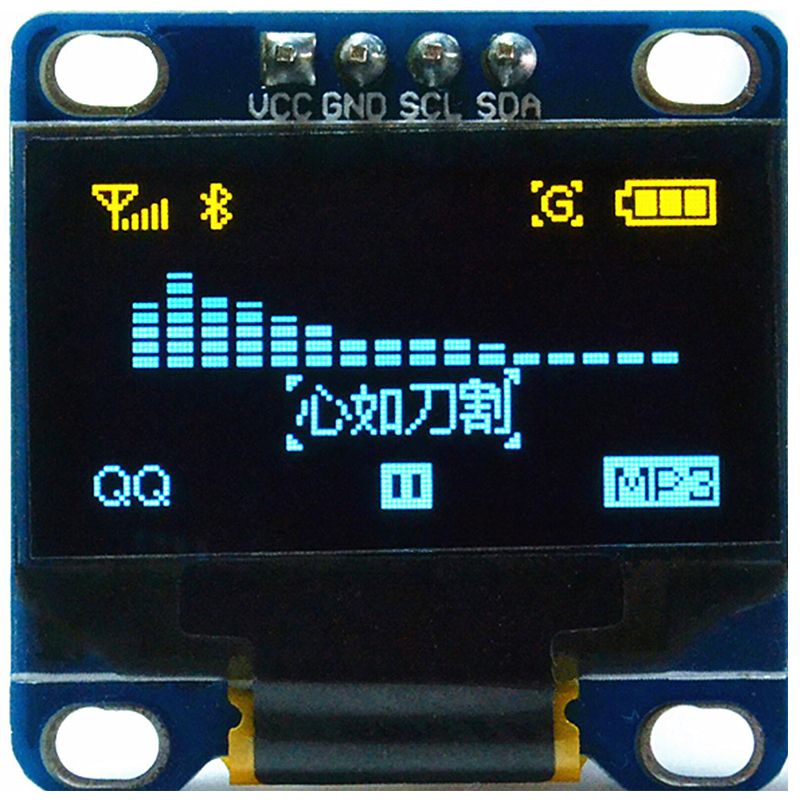

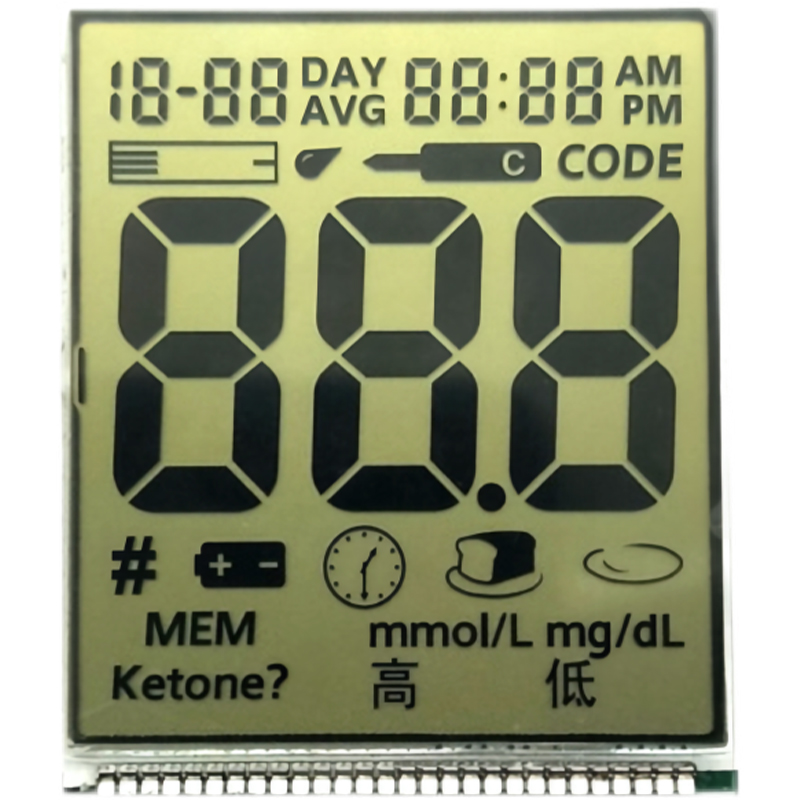

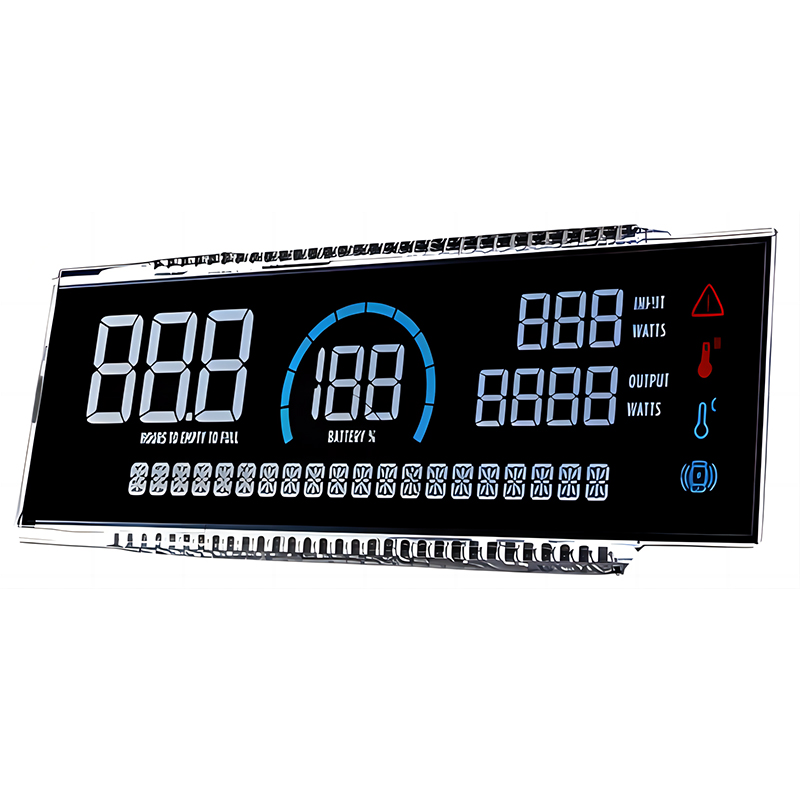

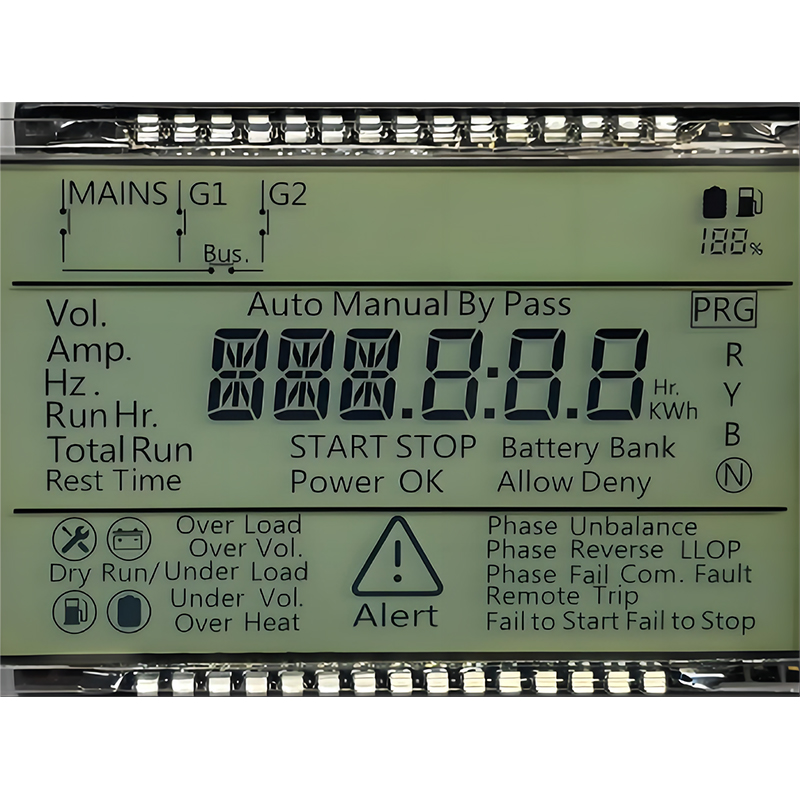

Xilinx SPI -Schnittstellein Ihren Projekten. Weitere Informationen zu qualitativ hochwertigen LCD-Displays und verwandten Komponenten finden Sie unter Besichtigung

Dalian Eastern Display Co., Ltd.(Referenzen werden hier auf Anfrage hinzugefügt, da bestimmte Datenblätter oder Dokumentationslinks erforderlich sind.)