El manejo de eficiencia de la salida de una transacción SPI (interfaz periférica en serie) es crucial para mantener la integridad de los datos y la estabilidad del sistema. Una salida mal administrada puede conducir a la corrupción de datos, errores del sistema e incluso daños en el hardware. Esta guía completa explora varias estrategias para lograr una limpieza y confiable Salida de la interfaz SPI, atiende a diferentes requisitos de aplicación y limitaciones de hardware.

SPI es un bus de comunicación full-dúplex sincrónico ampliamente utilizado en sistemas integrados. La transferencia de datos implica un dispositivo maestro que inicia la comunicación y varios dispositivos de esclavos que responden. Comprender el tiempo y la señalización involucrados es vital para la gestión adecuada de la salida. La terminación incorrecta puede conducir a una transferencia de datos incompleta o una recepción de datos erróneos.

Problemas comunes encontrados durante Salida de la interfaz SPI incluir:

El aspecto más crucial de una limpieza Salida de la interfaz SPI es la gestión adecuada de la línea Select (CS) de chips. Asegurar que la línea CS esté desertada (establezca alta) después de que la transferencia de bytes de datos finales sea primordial. Esto indica al dispositivo de esclavos que la comunicación está completa, lo que le permite terminar adecuadamente la transacción y evitar la transmisión de datos adicional. El momento de esta desertación es crítico y debe cumplir con las especificaciones específicas del dispositivo de esclavos.

El almacenamiento en búfer de datos efectivo en los lados maestros y esclavos juega un papel crucial. El almacenamiento en búfer adecuado ayuda a sincronizar la transferencia de datos y evita la pérdida de datos durante la salida. El maestro debe asegurarse de que todos los datos se envíen antes de la decisión CS, mientras que el esclavo debe confirmar que se reciben todos los datos.

La implementación de mecanismos de manejo de errores sólidos es esencial para confiables Salida de la interfaz SPI. Esto incluye verificar los errores de paridad, las suma de verificación u otras técnicas de validación. Si se detecta un error, se debe iniciar una estrategia de recuperación adecuada (como la retransmisión). Un sistema bien diseñado debe manejar con gracia errores y evitar fallas en cascada.

El diseño de hardware afecta significativamente Salida de la interfaz SPI fiabilidad. La coincidencia de impedancia adecuada, la integridad de la señal y la selección de componentes apropiados (como buffers y palancas de nivel) son críticas. El uso de componentes de alta calidad minimiza las reflexiones de la señal y garantiza la transmisión de datos confiable, reduciendo el riesgo de errores durante el proceso de salida.

Lo óptimo Salida de la interfaz SPI La estrategia depende en gran medida de las limitaciones específicas de la aplicación y el hardware. Factores como la velocidad de datos, el número de dispositivos de esclavos y los requisitos en tiempo real deben considerarse cuidadosamente. Un sistema que requiere un alto rendimiento de datos puede requerir diferentes estrategias que una priorización de bajo consumo de energía.

Analizar implementaciones exitosas de Salida de la interfaz SPI Las estrategias de varios sistemas integrados proporcionan ideas valiosas. El examen cuidadoso de estos ejemplos puede ayudar a los ingenieros a diseñar sistemas más robustos y confiables. Considere referirse a proyectos de código abierto o documentación técnica para ejemplos de implementación efectiva.

| Estrategia | Ventajas | Desventajas |

|---|---|---|

| Desertación inmediata de CS | Simple, rápido | Propenso a errores si la transferencia de datos no se completó |

| Desertación de CS retrasada con reconocimiento | Más confiable, garantiza la finalización de la transferencia de datos | Un poco más lento |

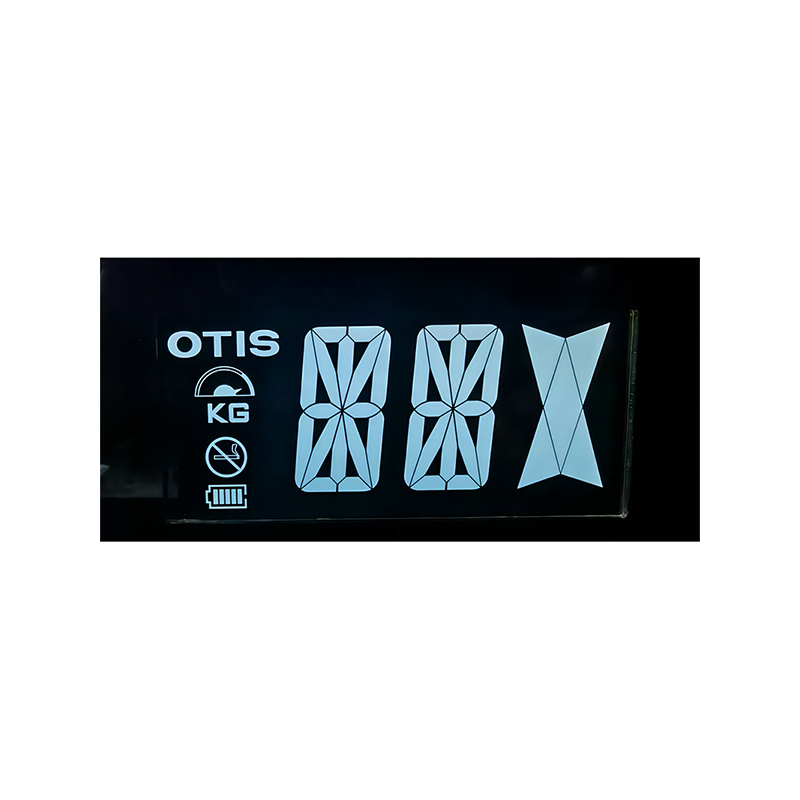

Recuerde consultar siempre las hojas de datos de sus dispositivos SPI específicos para obtener diagramas de tiempo detallados y prácticas recomendadas. Esto garantiza la compatibilidad y evita el comportamiento no intencionado durante el Salida de la interfaz SPI proceso. Para obtener más información sobre la tecnología y los componentes LCD, visite Dalian Eastern Display Co., Ltd.—Un proveedor líder de pantallas LCD de alta calidad.

Esta guía tiene como objetivo proporcionar una comprensión integral de Salida de la interfaz SPI estrategias. Al considerar cuidadosamente los diversos aspectos discutidos, los desarrolladores pueden diseñar sistemas integrados más robustos y confiables. Recuerde probar a fondo su implementación en diversas condiciones para garantizar su confiabilidad y estabilidad.