Esta guía proporciona una explicación detallada delInterfaz CPLD SPI, cubriendo sus fundamentos, aplicaciones prácticas y desafíos potenciales. Aprenda a configurar y utilizar de manera efectiva la comunicación SPI con CPLDS para varios diseños de sistemas integrados. Exploraremos diferentes aspectos, desde conceptos básicos hasta técnicas avanzadas, asegurando que tenga una comprensión sólida de esta interfaz crucial.

La interfaz periférica en serie (SPI) es un bus de comunicación full-dúplex sincrónico utilizado para la comunicación de corta distancia, principalmente en sistemas integrados. Se caracteriza por su simplicidad y velocidad, por lo que es una opción popular para conectar microcontroladores, sensores y otros periféricos. Una ventaja clave es su recuento de pin relativamente bajo en comparación con otras interfaces.

ElInterfaz CPLD SPITípicamente usa cuatro líneas de señal:

La configuración de hardware adecuada es fundamental para un exitosoInterfaz CPLD SPI. Esto implica seleccionar pines CPLD apropiados para cada señal, garantizar los niveles de voltaje correctos y considerar la integridad de la señal. La elección de CPLD dependerá de la complejidad de su aplicación y el rendimiento requerido.

La configuración del software implica programar el CPLD para responder correctamente a los comandos SPI. Esto a menudo incluye la configuración de registros específicos dentro del CPLD para manejar las señales de transferencia de datos y control. Los detalles variarán según la arquitectura de la CPLD y el lenguaje de programación elegido (por ejemplo, VHDL, Verilog).

Consideremos un escenario en el que está usando un CPLD Xilinx. El proceso implicaría:

Se pueden encontrar ejemplos detallados y fragmentos de código en la documentación de Xilinx y varios recursos en línea. Recuerde consultar las hojas de datos para su CPLD específico para asignaciones precisas de PIN y configuraciones de registro.

Diferentes modos SPI (modos 0-3) definen la polaridad y fase del reloj, influyendo en el momento de la transferencia de datos. Comprender estos modos es esencial para establecer la comunicación correcta. Su microcontrolador y CPLD deben configurarse para usar el mismo modo SPI.

La implementación de un manejo robusto de errores es crucial en cualquier sistema de comunicación. Esto podría incluir verificaciones de paridad, suma de verificación u otros mecanismos de detección y corrección de errores. Asegurar la integridad de los datos es primordial, especialmente en aplicaciones críticas.

Para aplicaciones de alta velocidad, optimizar la frecuencia del reloj y considerar cuidadosamente la integridad de la señal (por ejemplo, minimizar las longitudes de traza y usar la terminación adecuada) es vital. El SPI de alta velocidad puede requerir técnicas avanzadas como la señalización diferencial.

Solución de problemas de un mal funcionamientoInterfaz CPLD SPIA menudo implica la verificación sistemática de las conexiones de hardware, la configuración del software e integridad de la señal. La utilización de analizadores lógicos u osciloscopios puede ser invaluable para identificar problemas de tiempo o corrupción de datos.

Recuerde consultar siempre las hojas de datos de su CPLD y microcontrolador específicos para obtener información detallada e instrucciones específicas. Esta guía completa proporciona una base sólida para comprender y dominar elInterfaz CPLD SPI, empoderarlo para diseñar sistemas integrados robustos y eficientes.

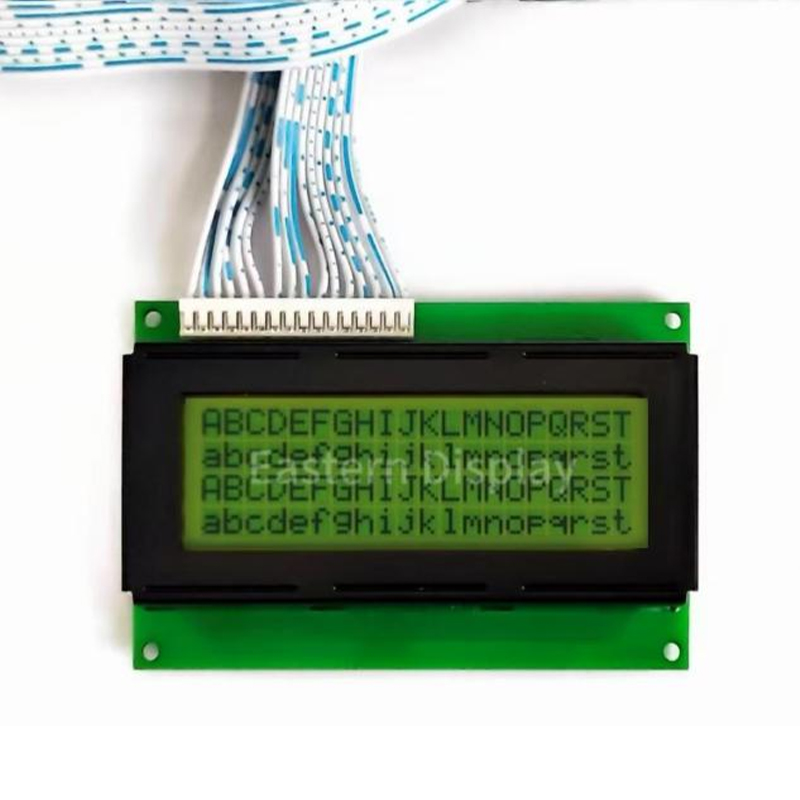

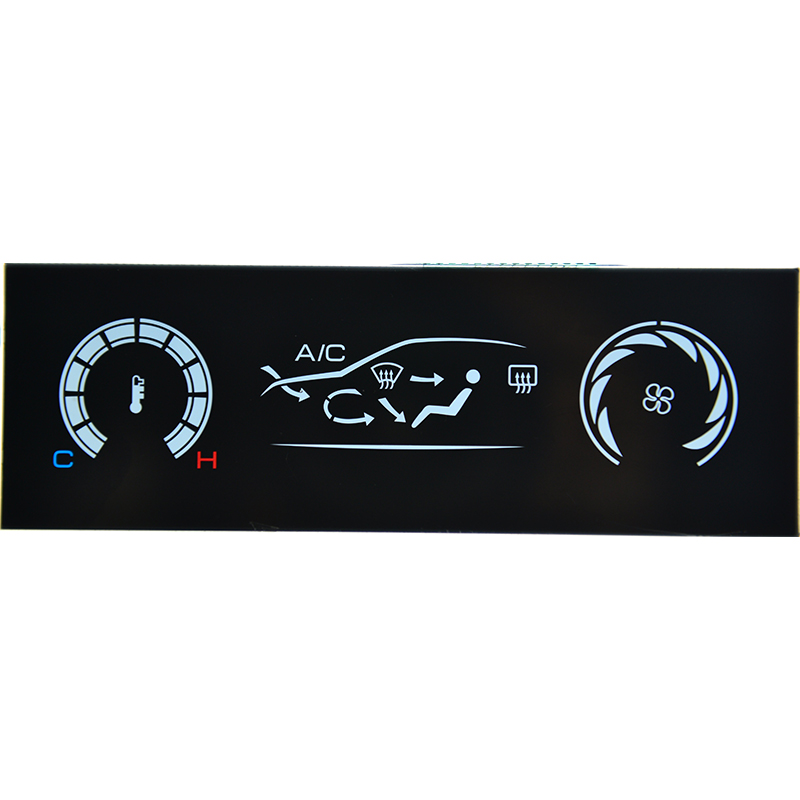

Para pantallas LCD de alta calidad para integrarse en sus proyectos de CPLD, considere explorar las opciones enDalian Eastern Display Co., Ltd.Ofrecen una amplia gama de pantallas adecuadas para diversas aplicaciones.