Esta guía proporciona una descripción completa de la interfaz periférica en serie (SPI) y su implementación en matrices de compuerta programables de campo (FPGA). Cubriremos los fundamentos de la comunicación SPI, exploraremos diferentes enfoques de diseño para las interfaces SPI basadas en FPGA y profundizaremos en ejemplos prácticos y consejos de solución de problemas. Aprenda a integrar eficientemente los periféricos SPI en sus proyectos FPGA y optimice el rendimiento para diversas aplicaciones.

El bus SPI es una interfaz de comunicación en serie síncrona y completa-dúplex ampliamente utilizada para la comunicación de corta distancia. Utiliza cuatro señales principales: MOSI (Master Out Slave In), Miso (Master in Slave Out), SCK (reloj en serie) y SS/CS (Slave Select/Chip Select). Comprender los roles de cada señal es crucial para exitososInterfaz FPGA SPIimplementación. Los datos se transmiten bit a bit, con la señal del reloj sincronizando la transferencia de datos. La línea de selección de esclavos se usa para seleccionar un dispositivo esclavo específico en el bus. Existen diferentes modos SPI, definidos por la configuración del reloj (CPOL) y fase (CPHA), influyendo en cómo se muestrean los datos en el borde del reloj.

Hay cuatro modos SPI principales (Modo 0 al Modo 3) determinados por la configuración CPOL y CPHA. Estas configuraciones afectan cuando los datos se muestrean durante el ciclo de reloj. Elegir el modo correcto es esencial para la comunicación con periféricos SPI específicos. La selección de modo incorrecto dará como resultado una transferencia de datos incorrecta. La siguiente tabla describe los diferentes modos:

| Modo | CPOL | Cpha | Descripción |

|---|---|---|---|

| Modo 0 | 0 | 0 | El reloj inactivo es bajo, los datos se muestrean en el borde ascendente. |

| Modo 1 | 0 | 1 | El reloj inactivo es bajo, los datos se muestrean en el borde de caída. |

| Modo 2 | 1 | 0 | El reloj inactivo es alto, los datos se muestrean en el borde ascendente. |

| Modo 3 | 1 | 1 | El reloj inactivo es alto, los datos se muestrean en el borde de caída. |

Implementando unInterfaz FPGA SPIimplica diseñar un módulo que interactúe con los periféricos SPI. Esto generalmente implica el uso de los bloques lógicos incorporados de FPGA para crear una máquina de estado que administra el protocolo de comunicación SPI. Considere el uso de núcleos IP proporcionados por su proveedor FPGA para un diseño simplificado y un rendimiento optimizado. Estos núcleos a menudo proporcionan características como el soporte de DMA para la transferencia de datos de alta velocidad.

El diseño se implementará utilizando Verilog o VHDL, dependiendo de su preferencia y las herramientas que está utilizando. El código administrará las cuatro señales SPI y manejará la transferencia de datos en función del modo SPI elegido. Una máquina de estado bien estructurada es crucial para manejar diferentes fases de la comunicación, como la afirmación seleccionada de chips, la transmisión de datos y la desertación de selección de chips. El manejo de errores y el diseño robusto son esenciales para garantizar una comunicación confiable.

Para la transferencia de datos de alta velocidad, considere técnicas como usar múltiples interfaces SPI o emplear características avanzadas ofrecidas por su FPGA, como interfaces seriales de alta velocidad dedicadas o controladores DMA. La consideración cuidadosa de la integridad de la señal también es crucial a frecuencias más altas para evitar la distorsión de la señal y los errores de datos.

Apoyar múltiples esclavos SPI requiere administrar múltiples líneas de selección de esclavos. Esto se puede lograr a través de un multiplexor o asignando instancias SPI separadas a cada esclavo. Administrar correctamente las señales de selección de esclavos es esencial para evitar conflictos entre múltiples dispositivos de esclavos.

DepuraciónInterfaz FPGA SPILos problemas pueden ser desafiantes. La utilización de analizadores lógicos y herramientas de depuración proporcionadas por su entorno de desarrollo FPGA son invaluables. Siempre verifique la configuración del modo SPI, las frecuencias del reloj y la integridad de la señal para garantizar la comunicación adecuada. Siguiendo las mejores prácticas para el diseño digital, como las convenciones de nombres de señales claras y el diseño modular, mejora en gran medida la capacidad de mantenimiento y la depugabilidad de su proyecto.

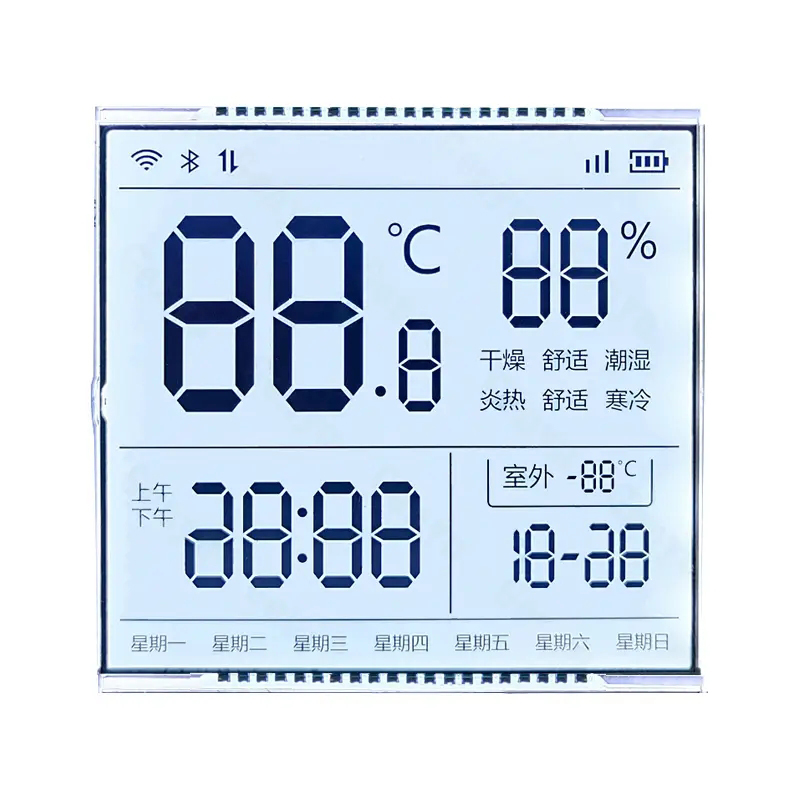

Para obtener más información sobre las pantallas LCD y las tecnologías relacionadas, puede encontrar los recursos enDalian Eastern Display Co., Ltd.útil. Ofrecen una amplia gama de soluciones de pantalla que a menudo utilizan la comunicación SPI.

Referencias:

1[Agregue su referencia aquí si usó alguna fuente externa]