Ce guide fournit une explication détaillée duInterface CPLD SPI, couvrant ses principes fondamentaux, ses applications pratiques et ses défis potentiels. Apprenez à configurer et à utiliser efficacement la communication SPI avec les CPLD pour divers conceptions de systèmes intégrés. Nous explorerons différents aspects, des concepts de base aux techniques avancées, en vous garantissant une solide compréhension de cette interface cruciale.

L'interface périphérique série (SPI) est un bus de communication synchrone et complet utilisé pour la communication à courte distance, principalement dans les systèmes intégrés. Il se caractérise par sa simplicité et sa vitesse, ce qui en fait un choix populaire pour connecter des microcontrôleurs, des capteurs et d'autres périphériques. Un avantage clé est son nombre de broches relativement faible par rapport aux autres interfaces.

LeInterface CPLD SPIutilise généralement quatre lignes de signal:

Une configuration matérielle appropriée est essentielle pour un succèsInterface CPLD SPI. Cela implique de sélectionner les broches CPLD appropriées pour chaque signal, d'assurer des niveaux de tension corrects et de considérer l'intégrité du signal. Le choix du CPLD dépendra de la complexité de votre application et des performances requises.

La configuration du logiciel implique la programmation du CPLD pour répondre correctement aux commandes SPI. Cela comprend souvent la configuration de registres spécifiques dans le CPLD pour gérer les signaux de transfert de données et de contrôle. Les détails varieront en fonction de l'architecture du CPLD et du langage de programmation choisi (par exemple, VHDL, Verilog).

Prenons un scénario où vous utilisez un Xilinx CPLD. Le processus impliquerait:

Des exemples détaillés et des extraits de code peuvent être trouvés dans la documentation Xilinx et diverses ressources en ligne. N'oubliez pas de consulter les fiches techniques pour votre CPLD spécifique pour des affectations de broches précises et des configurations d'enregistrement.

Différents modes SPI (modes 0-3) définissent la polarité et la phase de l'horloge, influençant le moment du transfert de données. Comprendre ces modes est essentiel pour établir une communication correcte. Votre microcontrôleur et CPLD doivent être configurés pour utiliser le même mode SPI.

La mise en œuvre d'une gestion des erreurs robuste est cruciale dans tout système de communication. Cela pourrait inclure des contrôles de parité, des sommes de contrôle ou d'autres mécanismes de détection et de correction d'erreur. Assurer l'intégrité des données est primordial, en particulier dans les applications critiques.

Pour les applications à grande vitesse, l'optimisation de la fréquence de l'horloge et considérant soigneusement l'intégrité du signal (par exemple, la minimisation des longueurs de trace et l'utilisation de terminaison appropriée) est vital. SPI à grande vitesse peut nécessiter des techniques avancées comme la signalisation différentielle.

Dépanner un défautInterface CPLD SPIImplique souvent une vérification systématique des connexions matérielles, de la configuration du logiciel et de l'intégrité du signal. L'utilisation d'analyseurs logiques ou d'oscilloscopes peut être inestimable pour identifier les problèmes de synchronisation ou la corruption des données.

N'oubliez pas de toujours consulter les fiches techniques de votre CPLD et microcontrôleur spécifiques pour des informations détaillées et des instructions spécifiques. Ce guide complet fournit une base solide pour comprendre et maîtriserInterface CPLD SPI, vous permettant de concevoir des systèmes intégrés robustes et efficaces.

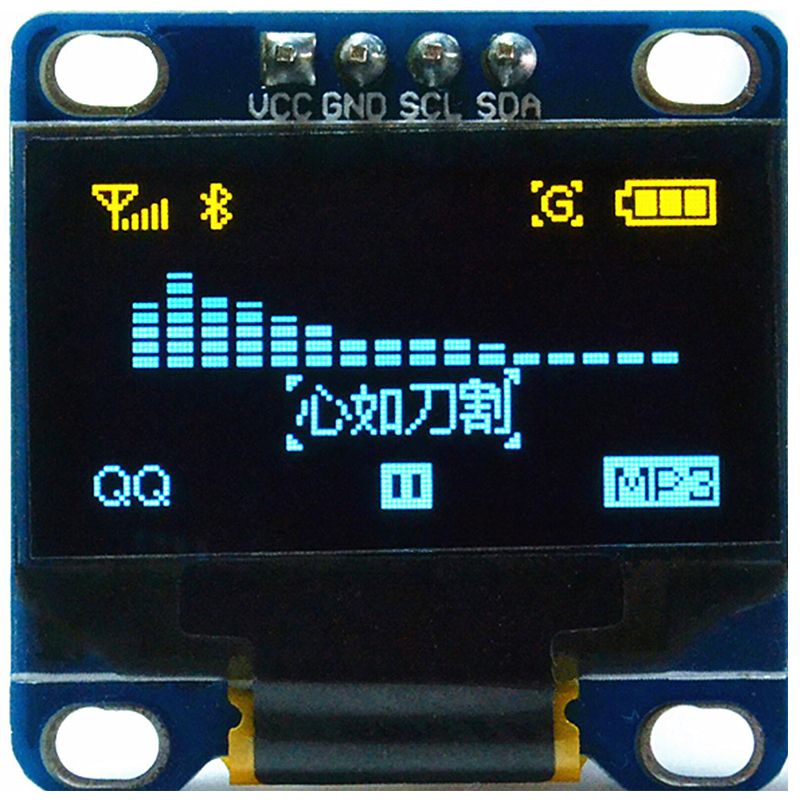

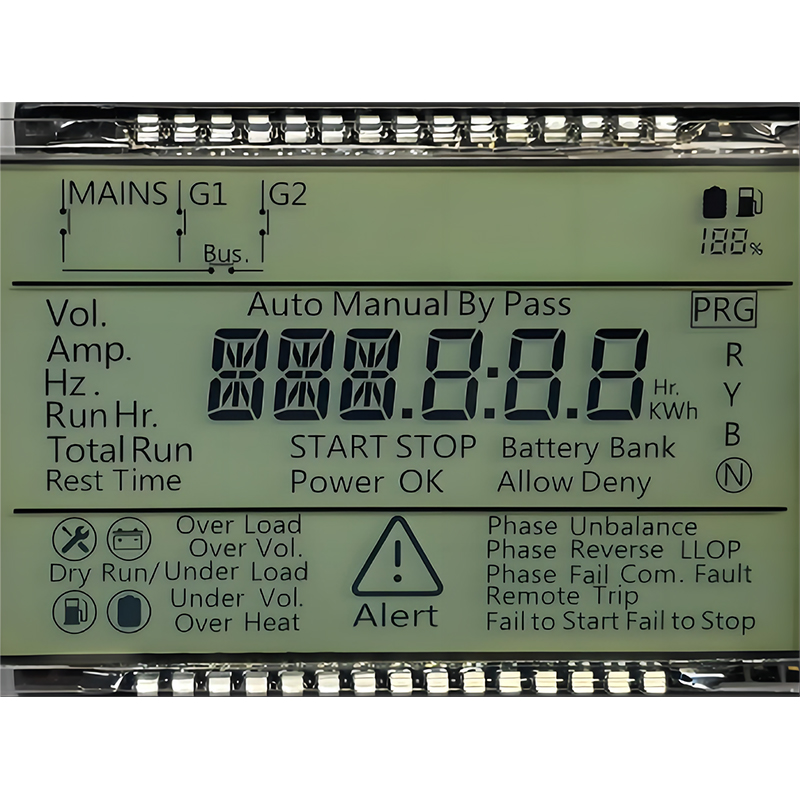

Pour les écrans LCD de haute qualité à intégrer dans vos projets CPLD, envisagez d'explorer les options àDalian Eastern Display Co., Ltd.Ils offrent une large gamme d'écrans adaptés à diverses applications.