Ce guide fournit un aperçu complet de l'interface périphérique série (SPI) et de son implémentation sur les tableaux de porte programmables sur le terrain (FPGA). Nous couvrirons les principes fondamentaux de la communication SPI, explorerons différentes approches de conception pour les interfaces SPI basées sur FPGA, et nous plonger dans des exemples pratiques et les conseils de dépannage. Apprenez à intégrer efficacement les périphériques SPI dans vos projets FPGA et à optimiser les performances pour diverses applications.

Le bus SPI est une interface de communication série synchrone et complète du duplex largement utilisée pour la communication à courte distance. Il utilise quatre signaux principaux: MOSI (Master Out Slave In), MISO (Master in Slave Out), SCK (Clock Serial) et SS / CS (Sellave Select / Chip Select). Comprendre les rôles de chaque signal est crucial pour réussirInterface FPGA SPImise en œuvre. Les données sont transmises bit à bit, le signal d'horloge synchronisant le transfert de données. La ligne de sélection d'esclaves est utilisée pour sélectionner un dispositif d'esclaves spécifique dans le bus. Il existe différents modes SPI, définis par les paramètres de polarité de l'horloge (CPOL) et de phase (CPHA), influençant la façon dont les données sont échantillonnées sur le bord de l'horloge.

Il y a quatre modes SPI principaux (mode 0 au mode 3) déterminé par les paramètres CPOL et CPHA. Ces paramètres affectent lorsque les données sont échantillonnées pendant le cycle d'horloge. Le choix du bon mode est essentiel pour la communication avec des périphériques SPI spécifiques. La sélection de mode incorrecte entraînera un transfert de données incorrect. Le tableau ci-dessous décrit les différents modes:

| Mode | Cpol | CPHA | Description |

|---|---|---|---|

| Mode 0 | 0 | 0 | L'horloge inactive est faible, les données sont échantillonnées sur le bord montant. |

| Mode 1 | 0 | 1 | L'horloge inactive est faible, les données sont échantillonnées sur le bord de la chute. |

| Mode 2 | 1 | 0 | L'horloge inactive est élevée, les données sont échantillonnées sur le bord montant. |

| Mode 3 | 1 | 1 | L'horloge inactive est élevée, les données sont échantillonnées sur le bord de la chute. |

Implémentation d'unInterface FPGA SPIimplique la conception d'un module qui interagit avec les périphériques SPI. Cela implique généralement d'utiliser les blocs logiques intégrés du FPGA pour créer une machine d'état qui gère le protocole de communication SPI. Envisagez d'utiliser les noyaux IP fournis par votre fournisseur FPGA pour une conception simplifiée et des performances optimisées. Ces noyaux fournissent souvent des fonctionnalités telles que le support DMA pour le transfert de données à grande vitesse.

La conception sera implémentée à l'aide de Verilog ou VHDL, selon vos préférences et les outils que vous utilisez. Le code gérera les quatre signaux SPI et gérera le transfert de données en fonction du mode SPI choisi. Une machine d'état bien structurée est cruciale pour gérer différentes phases de la communication, telles que l'affirmation de sélection de puces, la transmission de données et la désertion de sélection de puces. La gestion des erreurs et la conception robuste sont essentielles pour assurer une communication fiable.

Pour le transfert de données à grande vitesse, considérez des techniques telles que l'utilisation de plusieurs interfaces SPI ou l'utilisation de fonctionnalités avancées offertes par votre FPGA telles que les interfaces série à grande vitesse dédiées ou les contrôleurs DMA. Un examen attentif de l'intégrité du signal est également crucial à des fréquences plus élevées pour éviter la distorsion du signal et les erreurs de données.

La prise en charge de plusieurs esclaves SPI nécessite la gestion de plusieurs lignes de sélection d'esclaves. Cela peut être réalisé via un multiplexeur ou en attribuant des instances SPI distinctes à chaque esclave. Il est essentiel de gérer correctement les signaux de sélection des esclaves pour éviter les conflits entre plusieurs dispositifs d'esclaves.

DébogageInterface FPGA SPILes problèmes peuvent être difficiles. L'utilisation d'analyseurs logiques et d'outils de débogage fournies par votre environnement de développement FPGA est inestimable. Vérifiez toujours vos paramètres de mode SPI, vos fréquences d'horloge et votre intégrité du signal pour assurer une communication appropriée. Suivant les meilleures pratiques pour la conception numérique, telles que les conventions de dénomination des signaux clairs et la conception modulaire, améliore considérablement la maintenabilité et la débogDABILITÉ de votre projet.

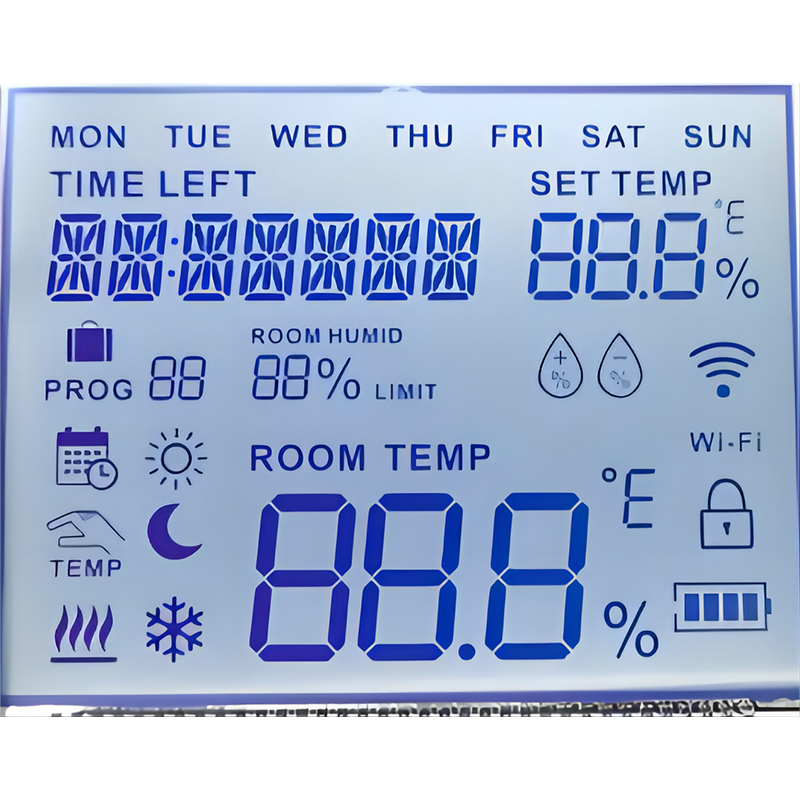

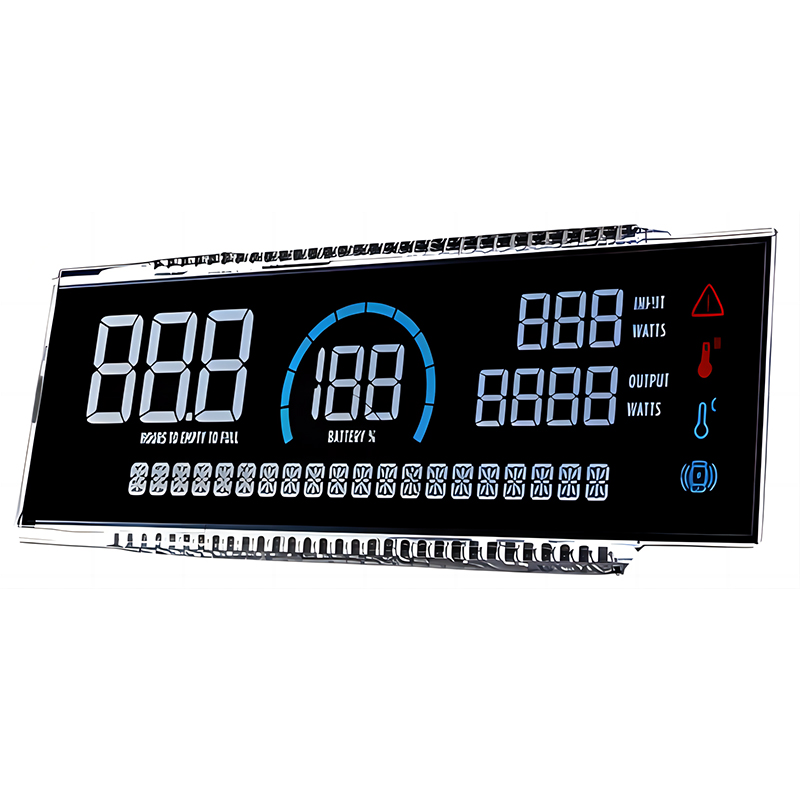

Pour plus d'informations sur les écrans LCD et les technologies connexes, vous pourriez trouver les ressources àDalian Eastern Display Co., Ltd.utile. Ils offrent une large gamme de solutions d'affichage qui utilisent souvent la communication SPI.

Références:

1[Ajoutez votre référence ici si vous avez utilisé des sources externes]