Ce guide fournit un aperçu complet de laInterface SPI, couvrant ses principes fondamentaux, applications, avantages, inconvénients et considérations pratiques. Découvrez comment fonctionne ce protocole de communication série polyvalente, ses différents modes et comment le mettre en œuvre efficacement dans vos projets. Nous explorerons des exemples du monde réel et offrirons des conseils pratiques pour maximiser les performances et le dépannage des problèmes communs.

L'interface périphérique série (Spice) est un bus de communication synchrone, complet et en duplex, largement utilisé pour la communication à courte distance, principalement dans les systèmes intégrés. Contrairement aux protocoles asynchrones comme I2C,SpiceUtilise un signal d'horloge pour synchroniser le transfert de données, permettant des débits de données plus rapides. Il s'agit d'une interface à quatre fils, généralement composée de quatre lignes: MOSI (Master Out Slave In), Miso (Master in Slave Out), SCK (Corloge série) et SS (Slave Select / Chip Select).

Le dispositif maître initie la communication en sélectionnant un appareil esclave spécifique à l'aide de la ligne SS. Il transmet ensuite des données sur la ligne MOSI, synchronisés par le signal d'horloge SCK. Le dispositif esclave reçoit ces données et répond en renvoyant des données sur la ligne Miso, également synchronisée par la SCK. La nature pleine duplex permet une transmission simultanée de données dans les deux sens, améliorant l'efficacité.

SpicePrend en charge différents modes de transfert de données, déterminés par la polarité de l'horloge (CPOL) et la phase d'horloge (CPHA). CPOL définit l'état d'inactivité du signal de l'horloge (élevé ou bas), tandis que CPHA définit lorsque les données sont échantillonnées (sur le bord montant ou descendant de l'horloge). Comprendre ces modes est crucial pour une bonne communication.

| Mode | Cpol | CPHA | Description |

|---|---|---|---|

| Mode 0 | 0 | 0 | Horloge inactive basse, données échantillonnées sur le bord montant |

| Mode 1 | 0 | 1 | Horloge inactive bas, données échantillonnées sur le bord de la chute |

| Mode 2 | 1 | 0 | Horloge inactive élevée, données échantillonnées sur le bord montant |

| Mode 3 | 1 | 1 | Horloge inactive élevée, données échantillonnées sur le bord de la chute |

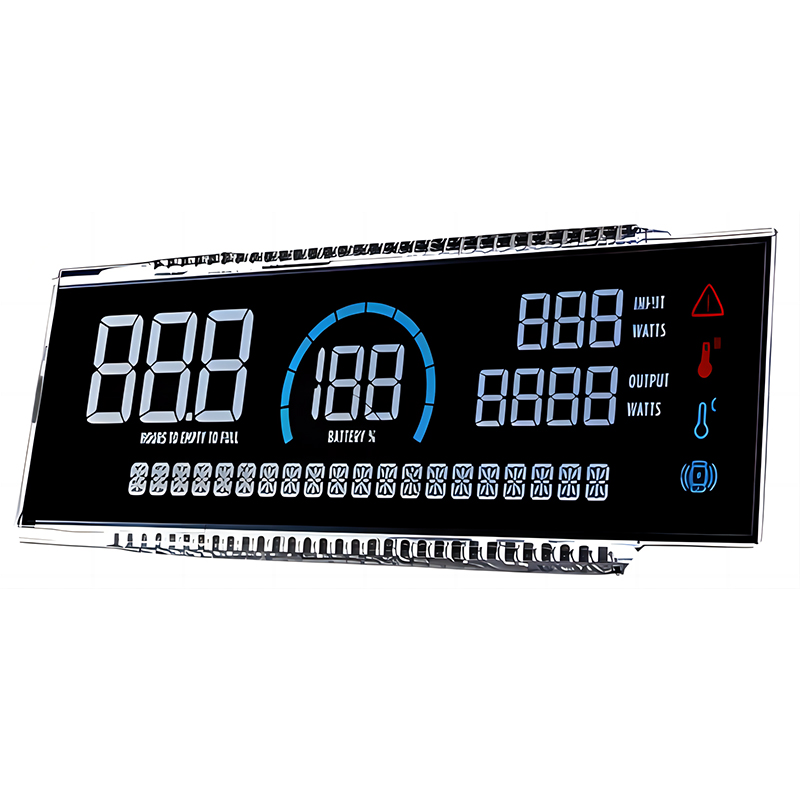

Spicetrouve des applications dans divers systèmes intégrés, notamment:

Implémentation d'unSpiceL'interface implique la configuration duSpicepériphérique sur votre microcontrôleur et sélection du mode approprié et de la vitesse d'horloge. Les détails de mise en œuvre spécifiques dépendront du microcontrôleur et du dispositif esclave. De nombreux microcontrôleurs fournissent des bibliothèques et un exemple de code pour simplifier le processus.

Problèmes courantsSpiceLa communication comprend des paramètres d'horloge incorrects, un mode de transfert de données incorrect et des défauts matériels. L'utilisation d'un analyseur logique peut aider à identifier ces problèmes. Examen attentif duSpiceLes signaux (MOSI, MISO, SCK, SS) peuvent identifier la source de l'erreur.

Ce guide fournit une compréhension fondamentale de laInterface SPI. Pour des informations plus approfondies, reportez-vous aux fiches techniques de votre microcontrôleur et appareils esclaves spécifiques. N'oubliez pas de toujours consulter la documentation du fabricant pour des spécifications détaillées et les meilleures pratiques.