3ワイヤのSPIインターフェイスの理解とトラブルシューティングIssuesthisの記事は、3ワイヤのSPIインターフェイスで発生する一般的な問題の理解と解決に関する包括的なガイドを提供します。 3線SPI通信、障害の一般的な原因、および実用的なトラブルシューティング手法の基本をカバーしています。 データの破損、クロックの同期などに関連する問題を特定して修正する方法を学びます。

4線のカウンターパートの独立したチップ選択(CS)ラインがない3線シリアル周辺インターフェイス(SPI)バスは、ユニークな課題を提示します。この簡素化されたバスアーキテクチャは、費用対効果が高いですが、バス管理と潜在的な障害点を慎重に検討する必要があります。 このガイドでは、共通を説明します 3線SPIインターフェイス 問題を発揮し、それらを診断して解決するための実用的な手順を提供します。 この通信プロトコルの複雑さを理解することは、組み込みシステムで信頼できるデータ送信を確保するために不可欠です。 効率的なデバッグのための手法を探求し、クロックの同期、データの整合性、および電力管理の重要な側面を強調します。 3線SPIインターフェイス 実装。

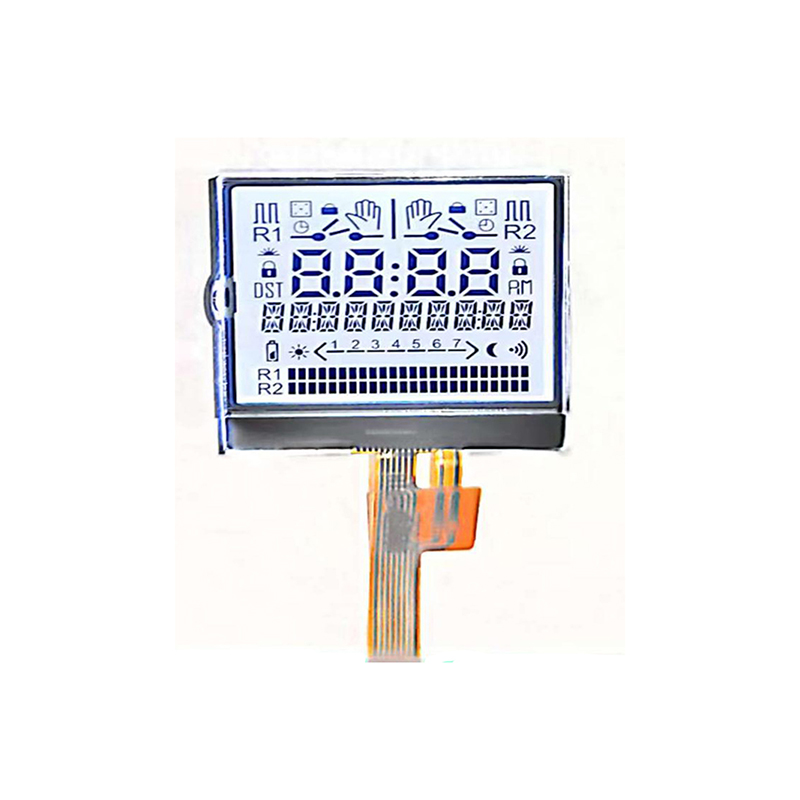

標準の4線SPIとは異なり、 3線SPIインターフェイス チップ選択(CS)行を省略します。 この単純化は、MOSI(奴隷のマスターアウトスレーブ)、味o(奴隷のマスター)、およびSCK(シリアルクロック)の3本のラインのみが使用されることを意味します。データ送信は、マスターとスレーブデバイス間の慎重なタイミングと同期に依存しています。 CSの欠如には、デバイスの選択と通信管理のための代替方法が必要であり、多くの場合、データストリーム内のスキームまたは特定のコマンドシーケンスのアドレス指定が含まれます。これにより、構成とデバッグの複雑さが向上します。

データは、SCKラインを使用してデータ転送を同期させるために、ビットごとにシュタリーに送信されます。マスターデバイスは、MOSIライン上のデータを送信することで通信を開始しますが、スレーブデバイスは味oラインにデータを送信することで応答します。 クロック極性(CPOL)とクロックフェーズ(CPHA)の設定を理解することは、コミュニケーションを成功させるために重要です。 これらの設定は、クロックエッジに対してデータがサンプリングされる場合に決定されます。

データの破損は頻繁に問題です 3線SPIインターフェイス 実装。これは、クロック信号の整合性の問題、ノイズ干渉、または誤ったタイミング構成によって引き起こされる可能性があります。 信号の完全性を慎重に検討することが最重要です。適切なシールドおよび接地技術は、ノイズ関連の問題を最小限に抑えることができます。 マスターデバイスとスレーブデバイスの両方の機能に対してクロック頻度とデータレートを確認することが不可欠です。 ロジックアナライザーを使用して信号波形を視覚的に検査すると、腐敗の原因を特定することができます。

適切な時計の同期は、成功するために最も重要です 3線SPIインターフェイス コミュニケーション。 マスターデバイスとスレーブデバイス間のクロック速度またはタイミングの不一致は、データエラーにつながります。 両方のデバイスのクロック周波数設定を再確認し、それらが互換性があることを確認します。外部クロックソースを使用する場合は、信号の整合性と安定性を確認してください。

専用のチップ選択ラインがなければ、デバイスの選択がより複雑になります。データストリーム内のアドレスデコードや特定のコマンドシーケンスの使用などの方法が使用されます。これらのアドレス指定またはコマンドスキームの誤った不明瞭さは、コミュニケーションの障害につながる可能性があります。 正しい実装を確保するために、関連するデバイスのデータシートを徹底的に確認します。

ロジックアナライザーは、デバッグするための貴重なツールです 3線SPIインターフェイス 問題。これにより、MOSI、味o、およびSCKラインのデジタル信号をキャプチャおよび分析することができ、タイミングの問題、データの腐敗、またはその他の異常を特定するのに役立ちます。 波形を視覚的に検査することにより、潜在的な問題をすぐに診断することができます。

不十分な電力または接地不足は、信号の完全性に悪影響を及ぼし、データエラーにつながる可能性があります。マスターデバイスとスレーブデバイスの両方に安定したクリーン電源があり、ノイズを最小限に抑えるために適切な接地が実装されていることを確認してください。

すべてのハードウェア接続を慎重にチェックして、MOSI、味o、およびSCKラインが正しく配線され、マスターとスレーブデバイスの両方の適切なピンに接続されていることを確認します。 接続が緩んだり、配線が誤っていたりすると、予測不可能な動作につながる可能性があります。損傷やショートパンツの兆候を視覚的に検査します。

最初からベストプラクティスを採用することは、堅牢で信頼性の高いものを構築するために重要です 3線SPIインターフェイス。 徹底的な計画とテストが不可欠です。 信号の完全性を改善し、エラーの可能性を減らすために、適切なシールドや終了などの堅牢な信号調整技術を使用することを検討してください。マスターデバイスとスレーブデバイスの両方の機能内にある設定を選択するデータレートとクロック頻度を慎重に検討します。 ロジックアナライザーとその他のデバッグツールを活用して、開発プロセスの早い段階で問題を特定して解決します。適切なプルアップまたはプルダウン抵抗を使用すると、信頼できる信号レベルを確保できます。 その他の技術サポートと高品質のディスプレイソリューションについては、利用可能なリソースを探索することを検討してください Dalian Eastern Display Co.、Ltd。

| トラブルシューティングステップ | アクション |

|---|---|

| 時計の同期を確認してください | ロジックアナライザーを使用して、マスターとスレーブの間のクロック信号の整合性と周波数の一致を確認します。 |

| データラインを検査します | ロジックアナライザーを使用して、エラーや矛盾についてMOSIおよび味oラインのデータ送信を観察します。 |

| 電源を確認します | マスターデバイスとスレーブデバイスの両方に十分で安定した電源を確認してください。 |