데이터 무결성 및 시스템 안정성을 유지하는 데 SPI (Serial Peripheral Interface) 트랜잭션에서 출구를 효율적으로 처리하는 것이 중요합니다. 제대로 관리되지 않은 출구는 데이터 손상, 시스템 오류 및 하드웨어 손상으로 이어질 수 있습니다. 이 포괄적 인 가이드는 깨끗하고 신뢰할 수있는 다양한 전략을 탐구합니다. SPI 인터페이스 출구, 다양한 응용 프로그램 요구 사항 및 하드웨어 제한을 제공합니다.

SPI는 임베디드 시스템에서 널리 사용되는 동기식 전이중 통신 버스입니다. 데이터 전송에는 통신을 시작하는 마스터 장치와 여러 슬레이브 장치가 응답합니다. 적절한 출구 관리에는 관련된 타이밍 및 신호를 이해하는 것이 중요합니다. 잘못된 종료는 불완전한 데이터 전송 또는 잘못된 데이터 수신으로 이어질 수 있습니다.

동안 발생하는 일반적인 문제 SPI 인터페이스 출구 포함하다:

깨끗한 것의 가장 중요한 측면 SPI 인터페이스 출구 Chip Select (CS) 라인의 적절한 관리입니다. 최종 데이터 바이트 전송이 가장 중요한 후 CS 라인이 탈퇴 (높은 설정)를 보장합니다. 이는 통신이 완료되었다는 슬레이브 장치에 대한 신호로 트랜잭션을 올바르게 종료하고 추가 데이터 전송을 방지 할 수 있습니다. 이 탈퇴의 타이밍은 중요하며 슬레이브 장치의 특정 사양을 준수해야합니다.

마스터와 슬레이브 측면의 효과적인 데이터 버퍼링은 중요한 역할을합니다. 적절한 버퍼링은 데이터 전송을 동기화하고 출구 중에 데이터 손실을 방지하는 데 도움이됩니다. 마스터는 CS를 탈퇴하기 전에 모든 데이터가 전송되도록하고, 슬레이브는 모든 데이터가 수신되었음을 확인해야합니다.

강력한 오류 처리 메커니즘을 구현하는 것은 신뢰할 수있는 데 필수적입니다 SPI 인터페이스 출구. 여기에는 패리티 오류, 체크섬 또는 기타 검증 기술 검사가 포함됩니다. 오류가 감지되면 적절한 복구 전략 (예 : 재전송)을 시작해야합니다. 잘 설계된 시스템은 오류를 우아하게 처리하고 계단식 고장을 방지해야합니다.

하드웨어 설계는 크게 영향을 미칩니다 SPI 인터페이스 출구 신뢰할 수 있음. 적절한 임피던스 매칭, 신호 무결성 및 적절한 구성 요소 (예 : 버퍼 및 레벨 시프터)의 선택이 중요합니다. 고품질 구성 요소를 사용하면 신호 반사가 최소화되고 신뢰할 수있는 데이터 전송이 보장되어 출구 프로세스 중에 오류의 위험이 줄어 듭니다.

최적 SPI 인터페이스 출구 전략은 특정 응용 프로그램 및 하드웨어 제약 조건에 크게 의존합니다. 데이터 속도, 슬레이브 장치 수 및 실시간 요구 사항과 같은 요소는 모두 신중하게 고려해야합니다. 높은 데이터 처리량이 필요한 시스템은 저전력 소비를 우선시하는 것과 다른 전략이 필요할 수 있습니다.

성공적인 구현 분석 SPI 인터페이스 출구 다양한 임베디드 시스템의 전략은 귀중한 통찰력을 제공합니다. 이러한 예를주의 깊게 조사하면 엔지니어가보다 강력하고 신뢰할 수있는 시스템을 설계하는 데 도움이 될 수 있습니다. 효과적인 구현의 예를 위해 오픈 소스 프로젝트 또는 기술 문서를 참조하십시오.

| 전략 | 장점 | 단점 |

|---|---|---|

| 즉각적인 CS 퇴적 | 간단하고 빠릅니다 | 데이터 전송이 완료되지 않은 경우 오류가 발생하기 쉽습니다 |

| 인정으로 CS 혼동 지연 | 보다 신뢰할 수있는 데이터 전송 완료를 보장합니다 | 약간 느리게 |

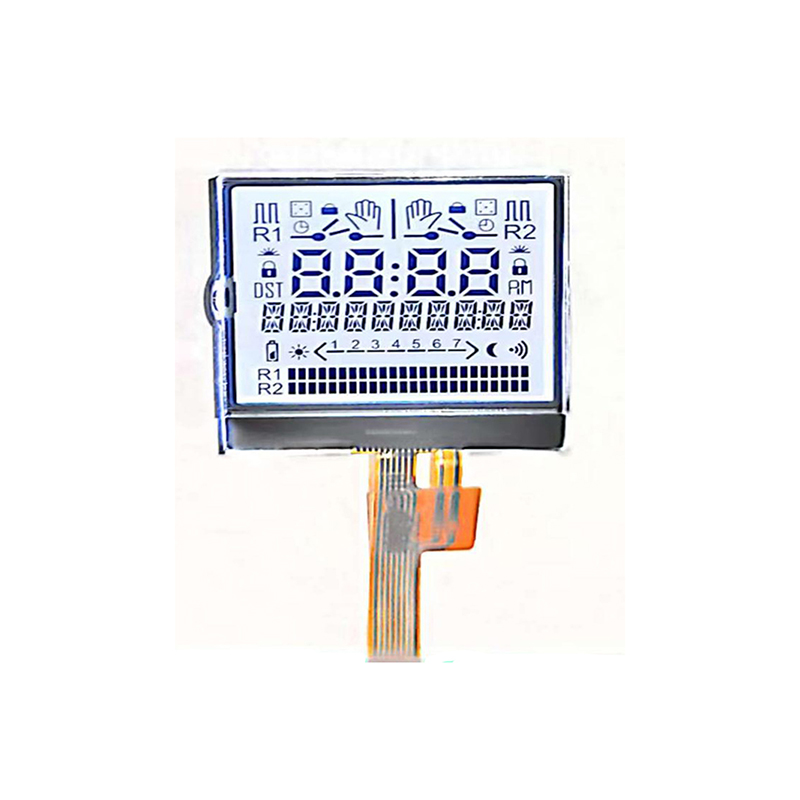

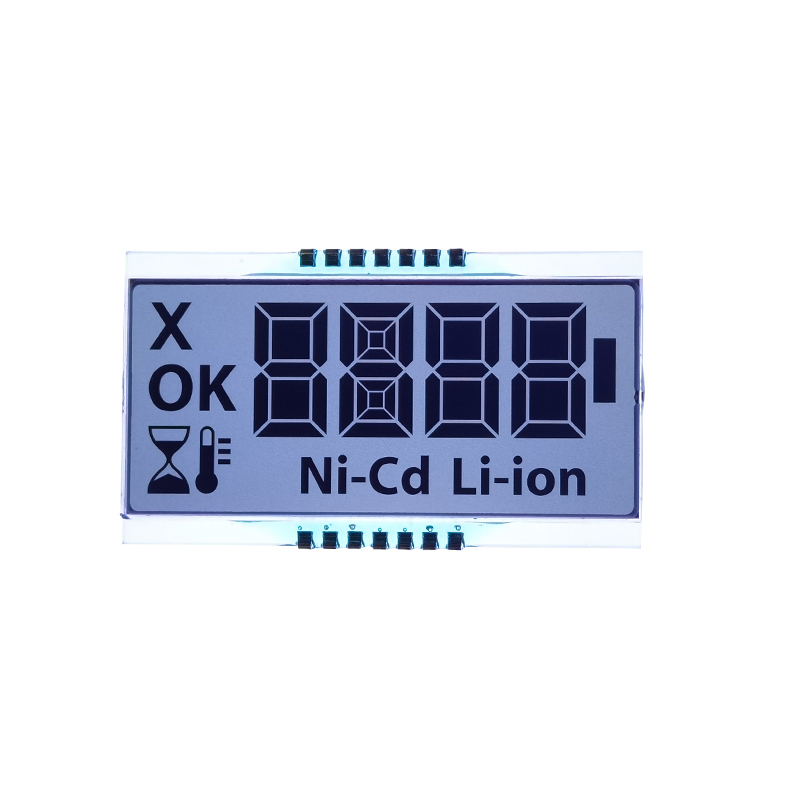

자세한 타이밍 다이어그램 및 권장 사례는 항상 특정 SPI 장치의 데이터 시트에 문의하십시오. 이것은 호환성을 보장하고 의도하지 않은 행동을 방지합니다 SPI 인터페이스 출구 프로세스. LCD 기술 및 구성 요소에 대한 자세한 내용은 방문하십시오 Dalian Eastern Display Co., Ltd.-고품질 LCD 디스플레이의 주요 제공 업체.

이 안내서는 포괄적 인 이해를 제공하는 것을 목표로합니다 SPI 인터페이스 출구 전략. 논의 된 다양한 측면을 신중하게 고려함으로써 개발자는보다 강력하고 신뢰할 수있는 임베디드 시스템을 설계 할 수 있습니다. 신뢰성과 안정성을 보장하기 위해 다양한 조건에서 구현을 철저히 테스트해야합니다.