This guide provides a comprehensive understanding of exiting SPI communication on an 8051 microcontroller. We'll cover various scenarios, potential issues, and best practices for ensuring clean and reliable 8051 SPI interface exit. We'll explore different approaches to managing the SPI peripheral after data transfer, emphasizing efficient resource utilization and preventing unexpected behavior.

The Serial Peripheral Interface (SPI) is a synchronous, full-duplex communication bus commonly used on microcontrollers like the 8051 for interfacing with various peripherals. Understanding how the 8051 SPI interface operates is crucial before tackling exit conditions. Key aspects include clocking, data transfer protocols (MOSI, MISO), and the role of chip select (CS) lines. Properly managing the CS line is often key to a successful 8051 SPI interface exit.

A typical SPI communication sequence involves asserting the chip select (CS) line, transmitting and receiving data, and finally de-asserting the CS line. The de-assertion of the CS line signals the end of communication and is a critical step in the 8051 SPI interface exit process. Failure to properly de-assert CS can lead to communication errors or conflicts with other SPI devices.

Different scenarios require different approaches to handle 8051 SPI interface exit. Let's explore some common situations and their solutions:

After a single byte or word of data is transferred, the CS line should be de-asserted immediately to signal the end of the transaction. This ensures that the SPI peripheral is properly released for other tasks. This is the most basic form of 8051 SPI interface exit.

When transferring multiple data bytes or words, the CS line remains asserted until all data has been exchanged. After the final data transfer, the CS line should be de-asserted to signal the 8051 SPI interface exit. Ensure proper synchronization between data transmission and CS line manipulation.

If interrupts are used to handle SPI communication, ensuring a clean 8051 SPI interface exit involves disabling interrupts appropriately before de-asserting the CS line. This prevents race conditions and ensures data integrity.

Problems with 8051 SPI interface exit can manifest in various ways. Common symptoms include data corruption, communication errors, and device malfunction.

Systematic debugging is essential. Use a logic analyzer or oscilloscope to visually inspect the SPI communication signals, paying close attention to the CS line transitions. This allows for precise identification of timing issues or incorrect CS management that might prevent a clean 8051 SPI interface exit.

Following best practices can significantly improve the reliability of your SPI communication and minimize problems related to 8051 SPI interface exit:

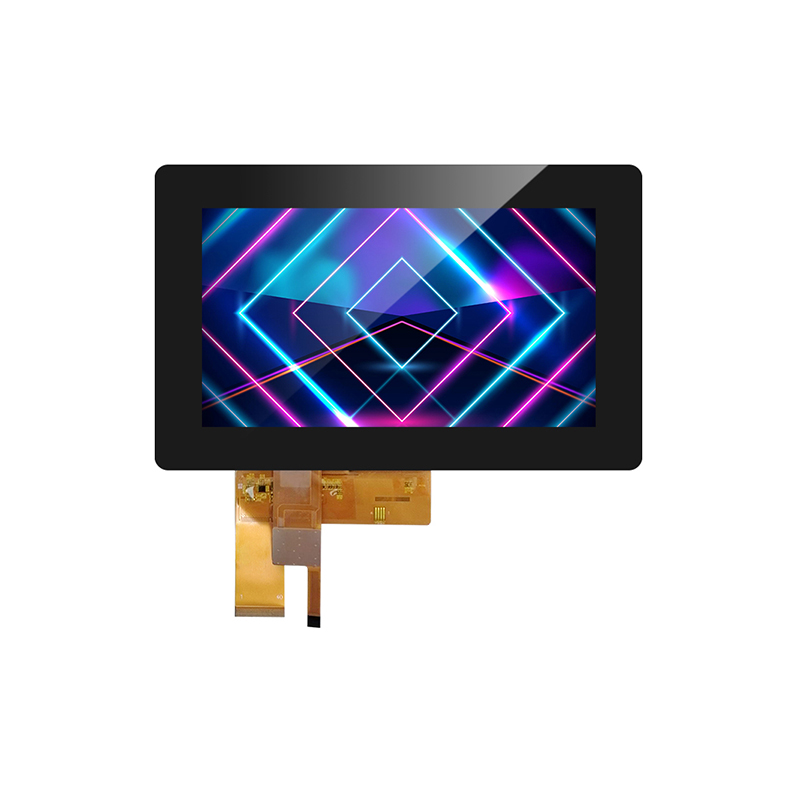

Remember, precise timing and proper CS management are vital for successful SPI communication. By understanding the intricacies of the 8051 SPI interface and implementing these best practices, you can ensure reliable and efficient data transfer in your embedded systems. For more information on high-quality display solutions for your embedded projects, consider exploring the possibilities offered by Dalian Eastern Display Co., Ltd., a leading provider of LCD modules and displays.