This guide explores effective methods for managing and exiting 3-wire SPI interfaces, focusing on clean disconnects and minimizing potential data loss or system instability. We'll cover various scenarios, best practices, and considerations for different hardware and software implementations.

A 3-wire SPI interface typically consists of three signals: MOSI (Master Out Slave In), MISO (Master In Slave Out), and SCK (Serial Clock). This simplified version omits the chip select (CS) line, requiring alternative methods for device selection and communication management.

Exiting a 3-wire SPI interface without proper handling can lead to issues like incomplete data transfers, corrupted data, or even hardware damage. The lack of a dedicated CS line necessitates careful synchronization and signal management during the exit process.

Software solutions focus on carefully sequencing communication commands to ensure a clean disconnect. This might involve sending a specific termination command or waiting for a predetermined period after the last data transfer.

Hardware solutions often involve incorporating external circuitry to manage the interface. This could include using a dedicated microcontroller pin to control the data flow or implementing a power-down sequence that cleanly disables the SPI communication lines.

Implementing a software timer allows the system to gracefully stop SPI communication after a set time. This prevents indefinite communication and resource conflicts. The timer's duration should be carefully chosen based on the expected data transfer time and potential communication delays.

Implement robust error handling mechanisms to detect and address potential issues during communication. This could include checksum verification or timeout checks to ensure data integrity and prevent crashes.

Accurate synchronization and timing are crucial for 3-wire SPI. Ensure the clock signal (SCK) is properly managed during the exit sequence to prevent data corruption or unexpected behavior. Proper timing is essential to ensure data is correctly transmitted and received.

How the power to the SPI device is managed during the exit procedure should be carefully considered. Sudden power loss can damage the device or cause data loss. A planned power-down sequence is often the best approach.

| Scenario | Solution |

|---|---|

| Data transfer interrupted unexpectedly | Implement timeout mechanisms and error handling to recover gracefully. |

| Device unresponsive | Implement a retry mechanism with increasing timeout periods, or consider a hardware reset if necessary. |

| System instability during exit | Thoroughly test and optimize the exit sequence, paying particular attention to signal timing and synchronization. |

Successfully exiting a 3-wire SPI interface requires careful planning and implementation. By employing the strategies and best practices outlined above, developers can significantly reduce the risk of data loss, system instability, and hardware damage. Remember that proper synchronization and error handling are crucial for robust and reliable communication.

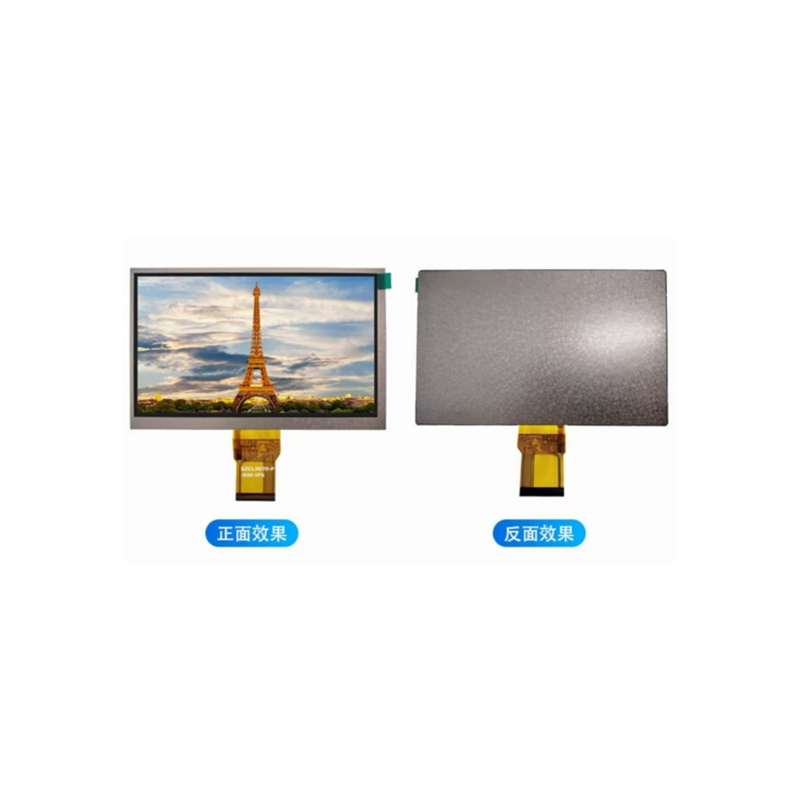

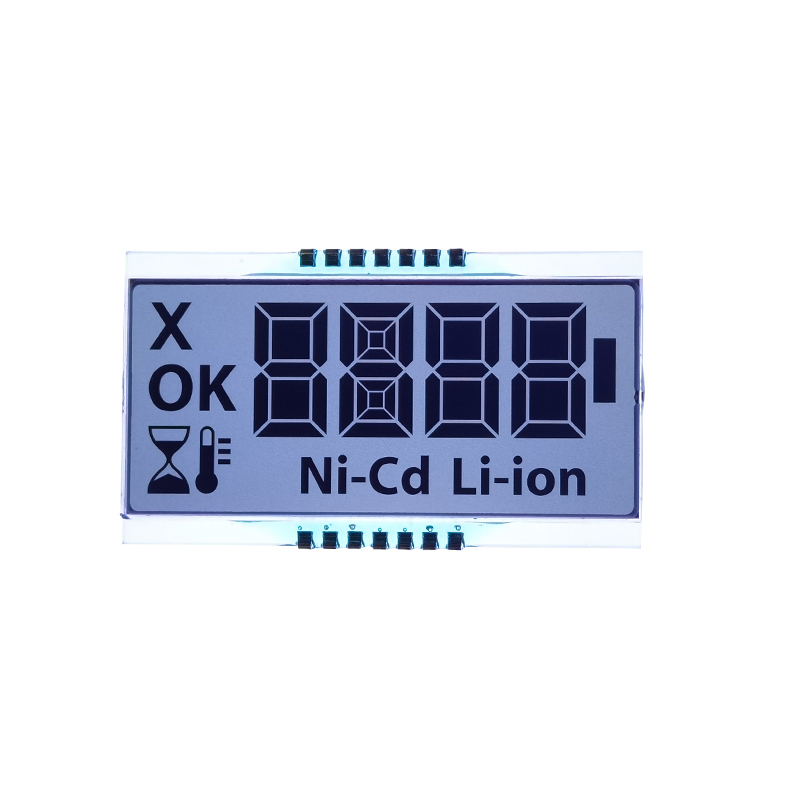

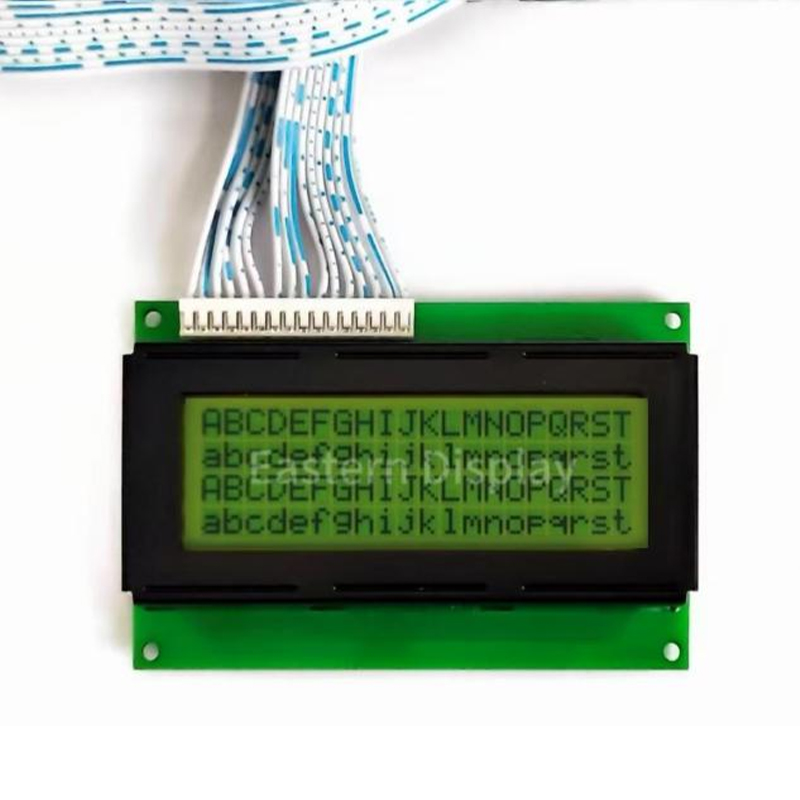

For more information on high-quality display solutions, consider exploring the resources available at Dalian Eastern Display Co., Ltd. They offer a wide range of advanced display technologies and can help you find the perfect solution for your needs.