The 8051 microcontroller's SPI interface, while powerful, requires careful management to ensure data integrity and prevent system instability. An unclean exit from an SPI transaction can lead to data corruption, unexpected behavior, and even hardware damage. This guide outlines best practices for managing the 8051 SPI interface exit, covering everything from proper clock control to handling potential errors.

Before diving into exit strategies, it's crucial to understand the basics of SPI communication on the 8051. SPI (Serial Peripheral Interface) is a synchronous, full-duplex communication protocol that uses a single master and multiple slaves. The 8051 typically acts as the master, controlling the clock and data flow. Key components involved include:

Understanding these signals is essential for implementing proper 8051 SPI interface exit procedures.

A clean 8051 SPI interface exit involves several key steps to ensure data integrity and prevent system issues. These include:

The most critical step is to deassert the SS pin (set it HIGH) after the data transfer is complete. This signals to the slave device that the communication is finished. Failing to deassert the SS pin can lead to continued communication, causing data corruption or system instability. The timing of this deassertion is crucial and should be carefully considered based on the specific slave device's datasheet. Delayed deassertion can lead to data errors.

After deasserting the SS pin, it's good practice to disable the SPI clock (SCLK) to prevent spurious data transmission. This helps ensure a clean break in the communication and avoids potential glitches.

Many SPI devices include error signals or status registers that can indicate communication issues. After an SPI transaction, it's crucial to check these signals to determine if any errors occurred. This proactive error checking can significantly improve the reliability of your system. Examples include checking for parity errors or CRC mismatches.

In some cases, communication issues may cause an SPI transaction to hang indefinitely. Implementing timeout mechanisms can help prevent such scenarios by terminating the transaction after a predefined period if no response is received. This mechanism ensures system responsiveness and prevents deadlocks. Proper timeout management is key to a robust 8051 SPI interface exit.

The following is a simplified example, illustrating the basic principles of a clean SPI exit. Remember to consult your specific hardware and slave device datasheets for accurate timing and control signal details. This code is intended for illustrative purposes only and may require modifications for specific applications.

// Deassert SSSS = 1;// Disable SPI clock (Specific register manipulation depending on your 8051 variant)// ...// Check for errors (Specific register checks depending on your SPI device)// ...// Handle potential errors appropriately// ...Despite implementing best practices, you might still encounter issues. Here are some common problems and solutions:

| Problem | Solution |

|---|---|

| Data corruption | Check SS deassertion timing, SPI clock configuration, and error flags. |

| System hangs | Implement timeout mechanisms, verify proper SS management, and check for hardware faults. |

| Intermittent errors | Investigate clock stability, noise interference, and power supply issues. |

Remember to always consult your specific 8051 microcontroller and SPI device datasheets for detailed information and timing requirements. Proper understanding of these specifications is essential for successful implementation.

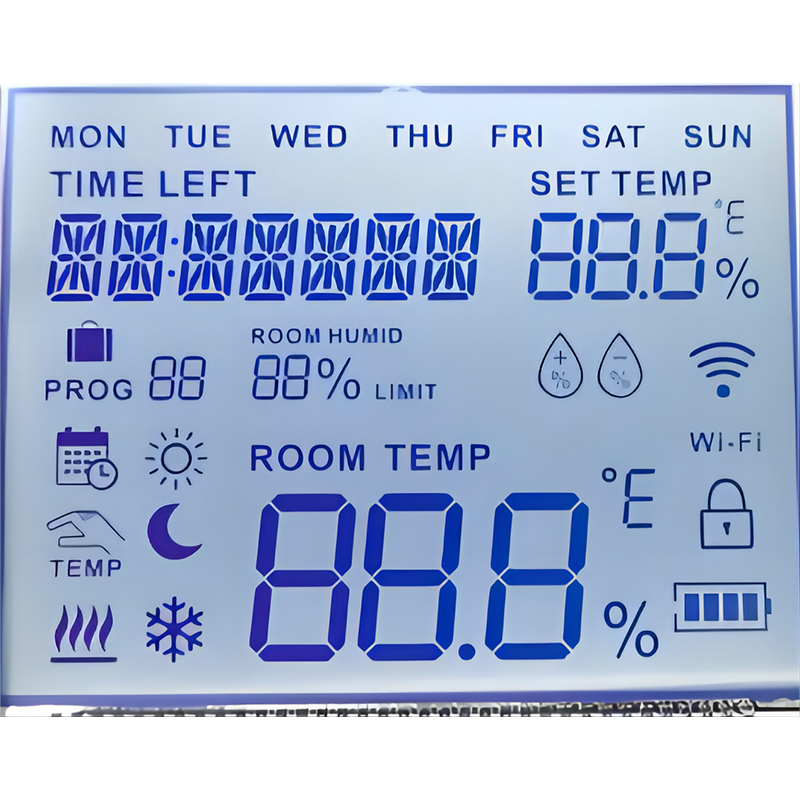

For high-quality LCD displays to integrate with your 8051 projects, consider exploring the options available from Dalian Eastern Display Co., Ltd. Their range of displays offers reliable performance and diverse functionalities.