Best Isolated SPI Interface Exit StrategiesThis article explores effective strategies for managing and optimizing the exit behavior of isolated SPI interfaces, focusing on minimizing latency and maximizing data integrity. We'll delve into various techniques, best practices, and considerations for different applications.

An isolated SPI interface, unlike standard SPI, incorporates isolation mechanisms to protect sensitive circuits from voltage spikes, ground loops, and electromagnetic interference (EMI). This isolation is crucial in applications where data integrity and system stability are paramount, such as industrial control systems, medical devices, and automotive electronics. Understanding how data transfers occur within this isolated environment is key to designing effective exit strategies.

Ensuring data integrity during the exit process is critical. Implement robust error detection and correction mechanisms, such as checksums or Cyclic Redundancy Checks (CRCs), to identify and handle corrupted data. Strategies for managing potential data loss or corruption in the event of an unexpected exit should also be integrated. A well-designed protocol can minimize these risks. Consider using advanced techniques such as forward error correction (FEC) for enhanced reliability.

Minimizing latency during the exit sequence is often a primary concern. Poorly designed exit routines can introduce significant delays. Techniques like efficient buffer management and optimized data transfer protocols are essential. Careful selection of hardware components, such as high-speed isolators, can further reduce latency. Consider using DMA (Direct Memory Access) to offload data transfer from the CPU, allowing for faster exit processing.

Proper power management is crucial, particularly in battery-powered applications. The Best Isolated SPI Interface Exit strategy should incorporate procedures to safely power down the SPI interface and its associated peripherals. This may involve carefully sequenced shutdown procedures to prevent data corruption or hardware damage. Proper power-sequencing is vital to prevent glitches.

In security-sensitive applications, the exit strategy should consider potential vulnerabilities. Ensure that the exit process doesn't leave the system vulnerable to unauthorized access or data breaches. Employ secure communication protocols and implement appropriate access control measures to protect against malicious activity. Cryptographic techniques can further enhance security during data transmission and the exit process.

Employing First-In, First-Out (FIFO) buffers can significantly enhance efficiency. These buffers allow for asynchronous data transfer, decoupling the SPI interface from the main processing unit, thereby reducing latency during the exit process. The choice of buffer size and implementation will depend on the specific application requirements and the anticipated data volume.

A software-based watchdog timer can provide an additional layer of safety. If the SPI interface fails to complete the exit sequence within a predetermined timeframe, the watchdog timer can trigger a reset, ensuring the system remains stable. This is crucial for handling unexpected scenarios and preventing system hang-ups.

Hardware solutions, such as dedicated SPI controllers with built-in error handling and power management capabilities, can significantly simplify the implementation of a robust Best Isolated SPI Interface Exit strategy. These controllers often include features that streamline the exit process, minimizing latency and enhancing reliability.

The optimal isolation method depends heavily on the application's requirements. Options range from optocouplers offering simple, cost-effective isolation to more advanced solutions like capacitive coupling or transformer-based isolation, which provide superior performance in noisy environments. Each method has its own trade-offs in terms of cost, bandwidth, and isolation voltage. The right choice is critical for maintaining signal integrity.

| Isolation Method | Advantages | Disadvantages |

|---|---|---|

| Optocouplers | Cost-effective, simple implementation | Limited bandwidth, potential for latency |

| Capacitive Coupling | High bandwidth, low latency | Higher cost, more complex design |

| Transformer-based Isolation | Excellent isolation, high bandwidth | Higher cost, larger size |

Selecting the best isolated SPI interface exit strategy requires a thorough understanding of the specific application and its requirements. By carefully considering data integrity, latency, power management, and security, developers can create robust and reliable systems.

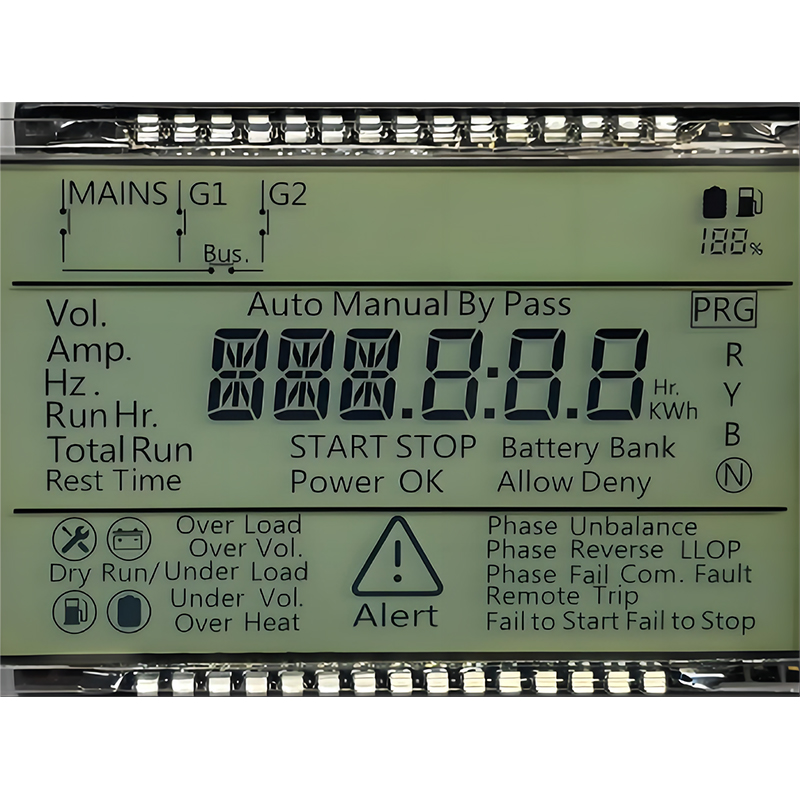

For more information on high-quality LCD displays that may be integrated into such systems, please visit Dalian Eastern Display Co., Ltd.