Successfully integrating a Serial Peripheral Interface (SPI) into your Xilinx-based design is crucial for many embedded applications. The choice of best Xilinx SPI interface depends heavily on your specific requirements, such as data rate, number of slaves, and complexity. This guide will navigate you through the process, providing insights into different methodologies and helping you make informed decisions.

Xilinx provides several SPI IP cores, each with its own strengths and weaknesses. Understanding these differences is paramount in selecting the best Xilinx SPI interface for your project. The most commonly used are:

The standard SPI IP core offers a basic implementation suitable for straightforward applications. It's easy to configure and integrate, making it ideal for simple projects with a low number of slaves and moderate data rates. However, for complex applications or high-speed data transfer, more advanced options may be necessary.

For applications demanding higher data throughput, the Quad SPI IP core offers significant advantages. This core supports four data lines simultaneously, dramatically increasing the data transfer rate. Consider using this for applications such as high-density flash memory interfaces where speed is critical. This option is a strong contender for the title of best Xilinx SPI interface in high-speed scenarios.

For more sophisticated designs, integrating the SPI core through the AXI bus provides greater flexibility and scalability. This enables seamless integration with other AXI-based components in your system, simplifying complex designs. This is often the preferred choice for large, intricate projects aiming for optimized performance and advanced features.

Optimizing your Xilinx SPI interface configuration is vital for achieving optimal performance. Key parameters include:

The clock speed significantly impacts data throughput. Carefully consider the maximum clock rate supported by both the SPI master (your Xilinx device) and the SPI slaves (peripherals). Always refer to the datasheets of your specific devices to avoid exceeding the limitations and causing malfunctions. Experimentation and careful selection are key to defining the best Xilinx SPI interface for your clock requirements.

SPI operates in different data modes, affecting the timing of data transmission. Choosing the correct mode ensures correct communication with your SPI slaves. Ensure compatibility between the master and slave devices for seamless operation.

The bit order (Most Significant Bit first or Least Significant Bit first) must match between the master and slave. Incorrect configuration leads to data corruption.

Even with careful planning, you may encounter challenges. Common issues include:

Data corruption frequently stems from clocking or mode mismatches. Double-check your configuration and ensure compatibility between the master and slave devices. Using a logic analyzer for debugging is invaluable in isolating the root cause.

Timing issues often arise from insufficient setup and hold times. Consult the Xilinx documentation and datasheets to ensure correct timing constraints are met.

Be aware of any limitations imposed by your specific Xilinx device and its capabilities. Carefully analyze the hardware specifications to determine the optimal performance achievable with your setup.

(This section would include a concise, practical example of implementing a simple SPI interface using VHDL or Verilog, along with relevant code snippets. Due to space constraints, a complete example is not included here. Refer to the Xilinx documentation for comprehensive examples and tutorials.)

Selecting and implementing the best Xilinx SPI interface requires careful consideration of various factors. By understanding the different IP cores, configuration options, and potential challenges, you can build robust and high-performing embedded systems. Remember to consult the Xilinx documentation for the most up-to-date information and support.

| SPI IP Core | Data Rate | Complexity |

|---|---|---|

| Standard SPI | Moderate | Low |

| Quad SPI | High | Medium |

| AXI-based SPI | High | High |

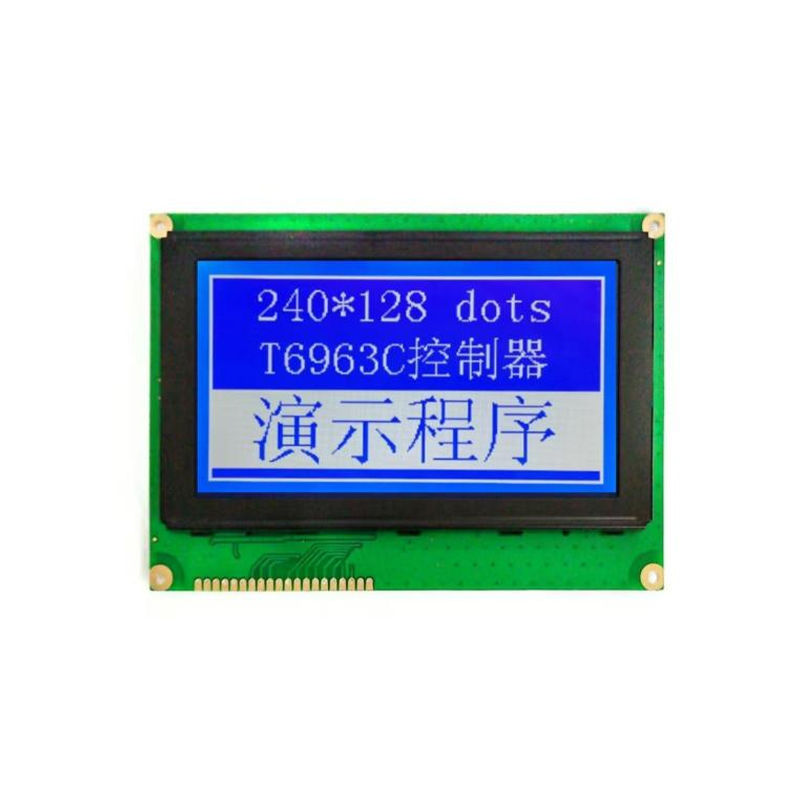

For more information on advanced display solutions, consider exploring Dalian Eastern Display Co., Ltd. – a leading provider in the industry. Their expertise in LCD technology complements the knowledge gained here, offering a holistic perspective on embedded system design.

1 Xilinx Documentation: [Insert relevant Xilinx documentation link here with rel=nofollow]