Choosing the right Xilinx SPI interface product can significantly impact your project's success. This guide delves into the key considerations when selecting an SPI interface solution for your Xilinx-based design, comparing different options and highlighting their strengths and weaknesses. Whether you're working on a high-speed data acquisition system, a low-power embedded device, or anything in between, understanding the nuances of SPI interfaces is crucial. We'll examine various aspects to aid in your decision-making process, helping you find the perfect fit for your application. This includes looking at different Xilinx families and their respective capabilities for SPI communication.

Xilinx offers several Intellectual Property (IP) cores for implementing SPI interfaces. The optimal choice depends on your specific requirements, including data rate, number of slaves, and power consumption. Popular choices often include the AXI4-Stream based cores which provide high bandwidth, and simpler, more resource-efficient cores for less demanding applications. Careful consideration of the trade-offs between performance and resource utilization is essential. Refer to the Xilinx Vivado IP catalog for the most up-to-date options. Selecting the correct IP core forms the foundation of a robust Xilinx SPI interface product implementation.

You can choose between hard and soft implementations of the SPI interface. Hard SPI uses dedicated hardware blocks within the FPGA, which generally leads to higher performance but consumes more resources. Soft SPI is implemented using logic resources, providing flexibility but usually at a lower data rate. The choice depends on your project's speed and resource constraints. Consider the balance between performance demands and resource availability when making your decision regarding hard versus soft SPI implementation within your Xilinx SPI interface product.

While specific product names are constantly evolving, the underlying principles remain consistent. Let's explore categories of solutions:

| Feature | High-Performance Solution (e.g., using AXI4-Stream) | Resource-Efficient Solution (e.g., simpler IP core) |

|---|---|---|

| Data Rate | Very High (dependent on FPGA and clock speed) | Moderate to Low |

| Resource Utilization | High | Low |

| Power Consumption | Higher | Lower |

| Complexity | Higher | Lower |

Table 1: Comparison of High-Performance and Resource-Efficient Xilinx SPI interface product solutions

Many applications require communication with multiple SPI slaves. Efficient management of multiple slaves necessitates careful consideration of addressing schemes and data synchronization. Xilinx IP cores often offer features to simplify this process, enabling streamlined communication with multiple devices through a single master. Efficient management of multiple SPI slaves is critical for complex Xilinx SPI interface product implementations.

Robust error handling is crucial for reliable SPI communication. Implementing mechanisms to detect and correct errors, such as parity checks or CRC codes, is essential for data integrity. These features contribute significantly to the overall reliability of your Xilinx SPI interface product.

Selecting the optimal Xilinx SPI interface product requires careful consideration of various factors, including data rate, resource utilization, power consumption, and the complexity of your application. By understanding the different options available and their trade-offs, you can make an informed decision to ensure the success of your project. Always consult the official Xilinx documentation for the most up-to-date information and best practices.

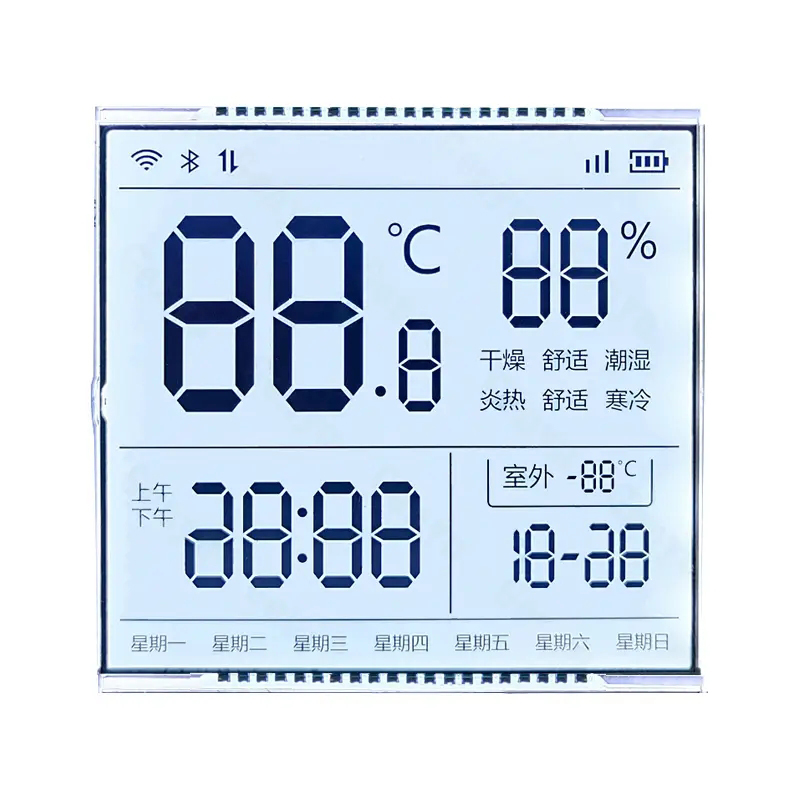

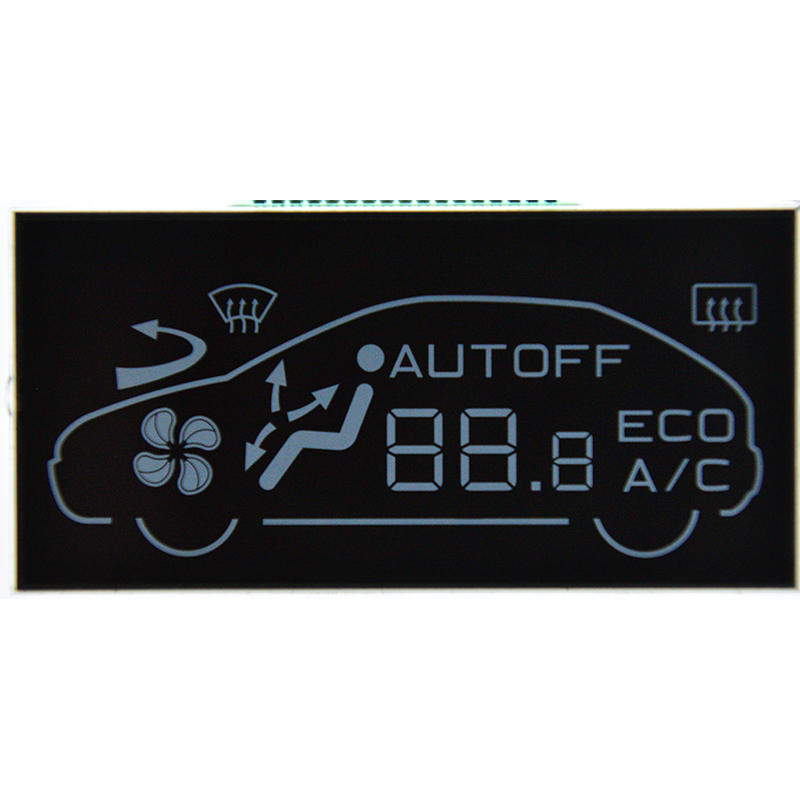

For high-quality displays to complement your Xilinx projects, explore the range of products offered by Dalian Eastern Display Co., Ltd.

1 Xilinx Website: [Insert relevant Xilinx documentation link here with rel=nofollow]