The quad SPI interface represents a significant advancement in Serial Peripheral Interface (SPI) technology, offering significantly increased data transfer rates compared to standard SPI. This guide delves into the intricacies of this interface, providing a comprehensive understanding of its architecture, benefits, and practical applications. We will also compare it with other SPI modes and highlight key considerations for successful implementation.

Before diving into the specifics of the quad SPI interface, it's crucial to understand the fundamental principles of SPI communication. SPI is a synchronous, full-duplex communication protocol that uses four wires: MOSI (Master Out Slave In), MISO (Master In Slave In), SCK (Serial Clock), and CS (Chip Select).

Standard SPI operates with a single data line for transmitting and receiving data. However, the quad SPI interface leverages all four lines simultaneously for data transmission, dramatically increasing data throughput.

In a quad SPI interface, both the master and slave devices transmit and receive data simultaneously across four lines. This parallel communication significantly accelerates data transfer speeds. The master device clocks the data transfer on the SCK line. The CS line selects which slave device communicates with the master. Each data bit is transferred on a separate line.

The data transfer process in quad SPI involves the master sending data on MOSI and receiving data on MISO concurrently. This parallel data flow contrasts with standard SPI's serial approach, leading to a considerable speed advantage. The exact timing and signal levels are defined by the specific SPI mode employed (Mode 0, Mode 1, Mode 2, Mode 3).

The primary advantage of quad SPI is its high speed. This makes it ideal for applications requiring fast data transfer, such as:

Compared to standard SPI, quad SPI often offers a four-fold increase in data transfer rates. This enhanced speed significantly reduces latency and improves overall system performance.

| Feature | Standard SPI | Dual SPI | Quad SPI |

|---|---|---|---|

| Data Lines | 1 | 2 | 4 |

| Speed | Lowest | Medium | Highest |

| Complexity | Lowest | Medium | Highest |

While quad SPI offers substantial benefits, successful implementation requires careful consideration of several factors, including hardware compatibility, clock speed limitations, and signal integrity.

Choosing appropriate hardware components that support quad SPI is paramount. Furthermore, maintaining signal integrity at higher clock speeds is crucial to prevent data corruption. Proper signal routing and termination techniques are essential to achieve reliable communication.

The high-speed nature of quad SPI makes it a preferred choice in various applications where rapid data transfer is vital. For instance, many high-performance microcontrollers and memory chips now incorporate quad SPI interfaces to accelerate data access times. This can result in significant performance gains in applications demanding efficient data handling.

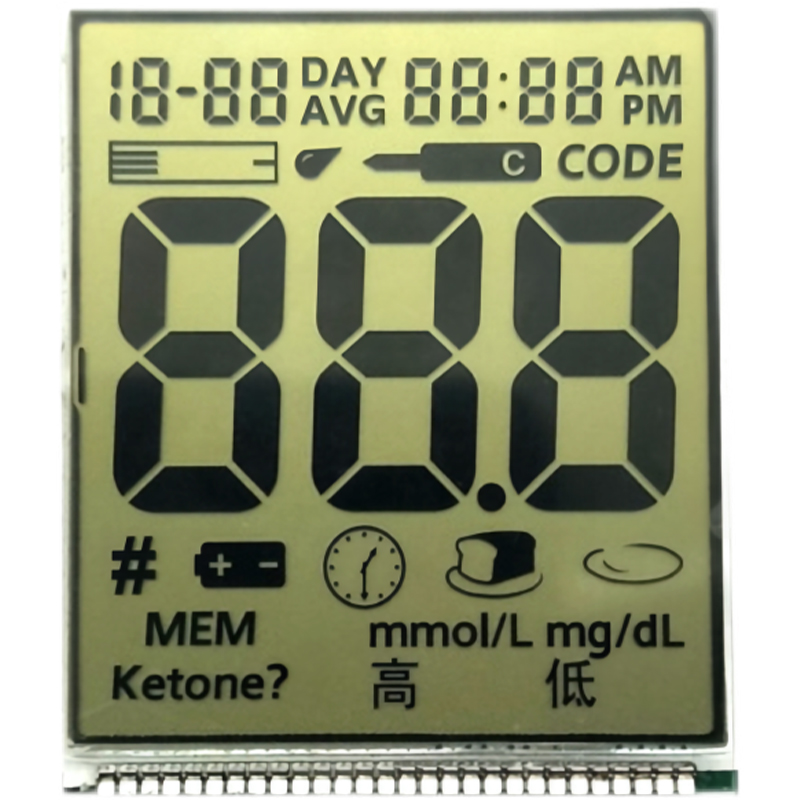

For example, in embedded systems, quad SPI is increasingly used to interface with flash memory. This allows for faster boot times and overall system responsiveness. In addition, high-resolution display controllers often utilize quad SPI to efficiently transfer large amounts of image data.

If you're looking for high-quality LCD displays for your projects, consider exploring the offerings from Dalian Eastern Display Co., Ltd. They provide a range of displays that could benefit from the fast data transfer capabilities of quad SPI.

This article provides a foundational understanding of the quad SPI interface. Further research into specific hardware and software implementations is recommended for practical application.