Sağlam ve verimli bir uygulama 2 telli SPI arayüzü Protokolün kapsamlı bir şekilde anlaşılmasını ve çeşitli faktörlerin dikkatle değerlendirilmesini gerektirir. Bu kılavuz, ortak tuzakları ele alan ve projelerinize kesintisiz entegrasyon için pratik çözümler sunan en iyi uygulamalara kapsamlı bir genel bakış sunar. Teknik yönleri araştıracağız, farklı yaklaşımları keşfedeceğiz ve çeşitli uygulamalar için performansı optimize etmeyi tartışacağız.

Standart SPI (seri periferik arayüz) protokolü tipik olarak dört kablo kullanır: MOSI (Master Out Slave In), MISO (köle dışarıda master), SCK (CLACK) ve CS (Chip Select). Ancak, 2 telli SPI arayüzü MOSI ve MISO çizgilerini tek bir çift yönlü çizgiye birleştirerek bunu basitleştirir. Bu, kablo karmaşıklığını azaltır ve bant genişliği gereksinimlerinin daha az talepkar olduğu uygulamalar için uygundur. Bu yöntem genellikle güvenilir veri iletimini sağlamak için dikkatli zamanlama kontrolü gerektirir.

| Özellik | Avantaj | Dezavantaj |

|---|---|---|

| Kablolama | Azaltılmış kablolama karmaşıklığı | Tek çift yönlü çizgi gürültüye daha duyarlı olabilir |

| Maliyet | Potansiyel olarak daha düşük bileşen maliyeti | Mikrodenetleyicide daha sofistike zamanlama yönetimi gerektirebilir |

| Hız | Düşük bant genişliğinde uygulamalar için yeterli olabilir | 4 telli SPI ile karşılaştırıldığında daha düşük veri aktarım hızları |

Tablo 1: 2 telli ve 4 telli SPI karşılaştırması

Uygulamak 2 telli SPI arayüzü Genellikle, mikrodenetleyicinin veri hatlarını doğrudan kontrol ettiği dikkatli bit banglama tekniklerini içerir. Bu, veri bozulmasını önlemek için hassas zamanlama kontrolü gerektirir. Birçok mikrodenetleyici donanım SPI çevre birimleri sunar, ancak bunlar doğrudan desteklemeyebilir 2 telli SPI. Bu nedenle, yazılım tabanlı uygulamalar sıklıkla gereklidir.

Bir sensörle iletişim kurmak için bir AVR mikrodenetleyici kullandığınız bir senaryoyu düşünelim. 2 telli SPI arayüzü. İlgili GPIO pinlerini saat ve veriler için çıkışlar olarak yapılandırmanız, her bit iletiminin zamanlamasını titizlikle yönetmeniz ve alınan verileri dikkatlice yorumlamanız gerekir. Kütüphaneler veya örnek kodu genellikle kesin zamanlama ve veri işlemesine yardımcı olmak için mevcuttur. Bit manipülasyonu ve GPIO yapılandırması ile ilgili özellikler için mikrodenetleyicinin veri sayfasına danışmayı unutmayın.

Karşılaşılan ortak sorunlar 2 telli SPI arayüzleri Gürültü hassasiyeti ve zamanlama hataları ekleyin. Gürültü verileri bozabilirken, yanlış zamanlama kaçırılan bitlere veya senkronizasyon sorunlarına yol açabilir. Dikkatli PCB düzeni ve korumalı kablolama gürültüyü azaltabilir. Zamanlama parametrelerini doğrulamak ve güvenilir çalışmayı sağlamak için kapsamlı test ve simülasyon çok önemlidir. Diferansiyel sinyal kullanma gibi gelişmiş teknikler gürültü bağışıklığını artırabilir. Sorun giderme amacıyla sinyalleri incelemek için bir mantık analizörü kullanmayı düşünün.

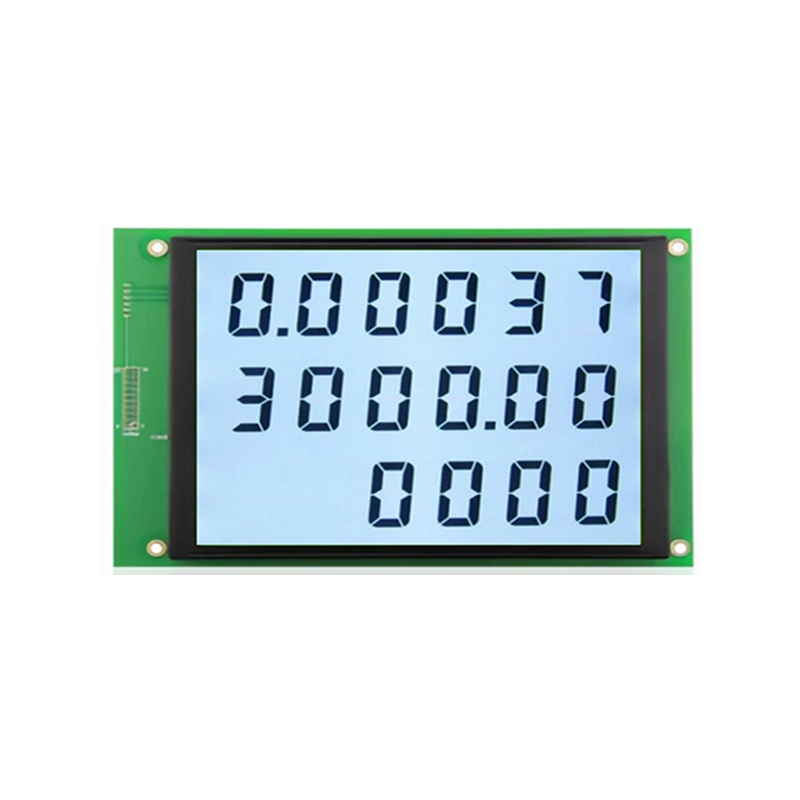

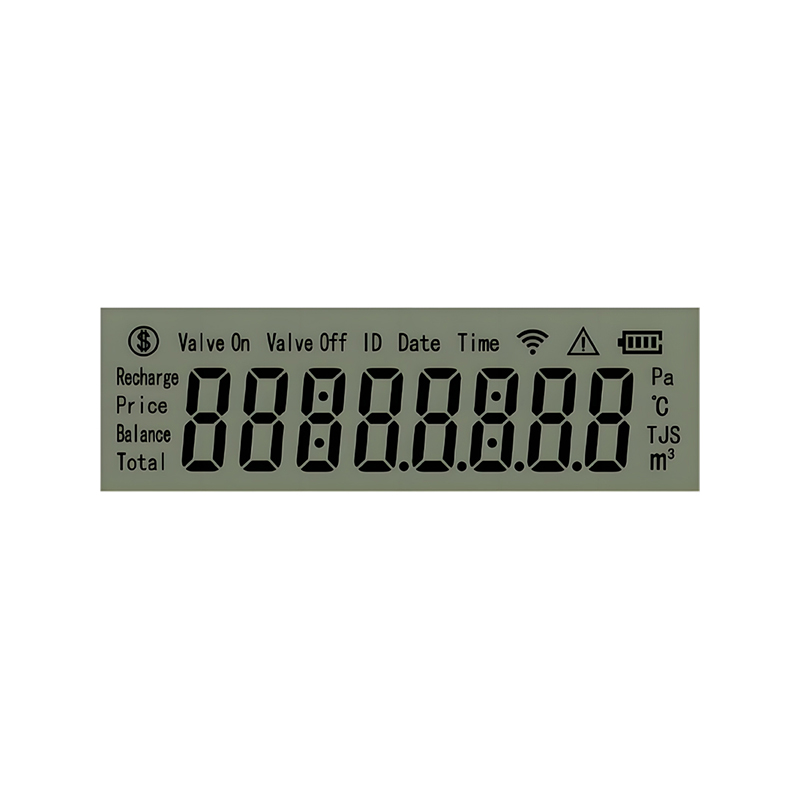

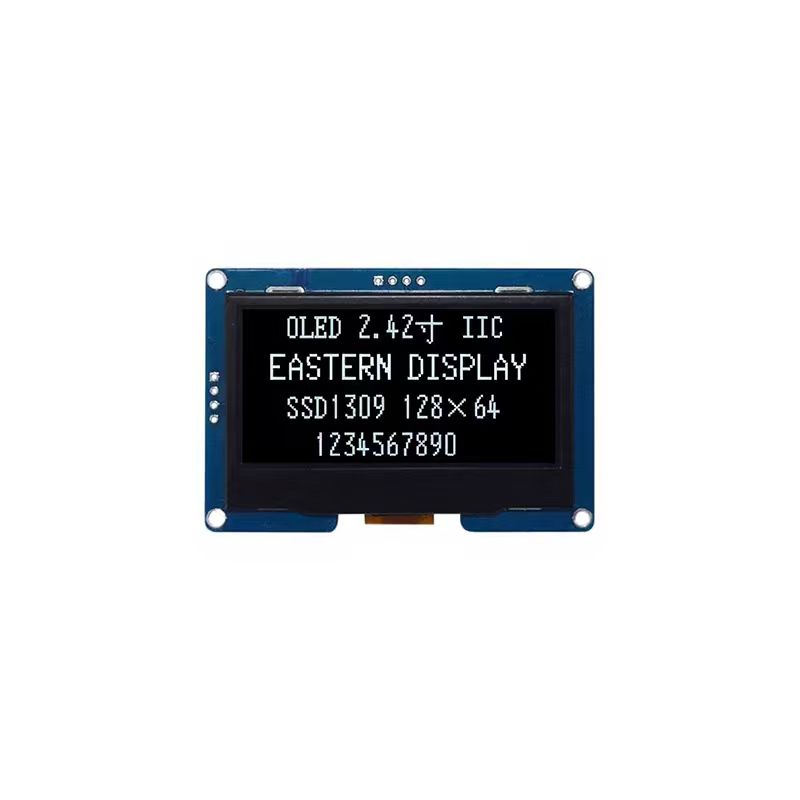

Başarıyla uygulamak 2 telli SPI arayüzü Protokolün nüanslarının ve uygulamanın özel gereksinimlerinin kapsamlı bir şekilde anlaşılmasını gerektirir. Avantajları ve dezavantajları dikkatlice göz önünde bulundurarak, potansiyel sorunları anlayarak ve en iyi uygulamaları kullanarak sağlam ve verimli bir çözüm yaratabilirsiniz. 4 telli SPI ile karşılaştırıldığında bazı zorluklar sunarken, sadelik ve azaltılmış kablolama onu uygun uygulamalar için değerli bir seçenek haline getirir. Yüksek kaliteli LCD ekranlar ve diğer bileşenler için, saygın bir tedarikçi ile ortaklık kurmayı düşünün Dalian Eastern Display Co., Ltd. Kesintisiz entegrasyon sağlamak için.